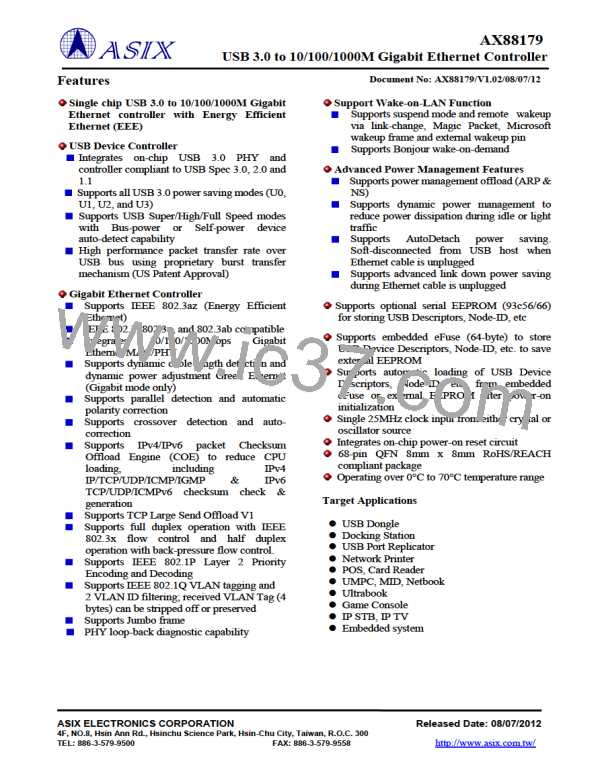

AX88179

USB 3.0 to 10/100/1000M Gigabit Ethernet Controller

2.2 Hardware Setting For Operation Mode and Multi-Function Pins

The following hardware settings define the desired operation mode and some multi-function pins. The logic level shown on

setting pin below is loaded from the chip I/O pins during power on reset based on the setting of the pin’s pulled-up (as logic

‘1’) or pulled-down (as logic ‘0’) resister on the schematic.

EEPROM Offset 05h or eFuse Offset 18h, Flag[4]: Defines the multi-function pin GPIO_0 / PME

GPIO_0 is a general purpose I/O normally controlled by vendor commands. Users can change this pin to operate as a PME

(Power Management Event) for remote wake up purpose. Please refer to Section 4.1.2 “Flag” of bit 4 (PME_PIN).

GPIO_1 pin: Determines whether this chip will go to Default WOL Ready Mode after power on reset. The WOL stands

for Wake-On-LAN.

GPIO_1

Description

Normal operation mode (default, see Note 1).

Enable Default WOL Ready Mode. Notice that the external pulled-up resistor must be 4.7Kohm.

For more details, please refer to APPENDIX A. Default Wake-On-LAN (WOL) Ready Mode

0

1

Note 1: This is the default with internal pulled-down resistor and doesn’t need an external one.

GPIO_2 pin: Determines whether SSTX+ swaps with SSTX- and SSRX+ swaps with SSRX- for USB3.0 PHY.

GPIO_2

Description

0

1

No swapping (default, see Note 1).

Enable swapping. Notice that the external pulled-up resistor must be 4.7Kohm.

MFA_3 ~ MFA_0 pins: There are 4 multi-function pins for LED display purpose and as GPIO controlled by vendor

command PIN Control Register MFA_EN (Section 6.2.2.23).

Section

4.1.6

LED_3

Section

6.2.1.9 &6.2.1.10

MFAIO_3

PIN Name

Default definition

MFA_3

LED_USB indicator

(Super-speed)

MFA_2

MFA_1

MFA_0

Programmable LED

(Link 10/100/1000+Active)

Programmable LED

(Link 10/100/1000)

Programmable LED

(Active)

LED_2

LED_1

LED_0

MFAIO_2

MFAIO_1

MFAIO_0

Table 2

: MFA_3 ~ MFA_0 pin configuration

11

Copyright © 2011-2012 ASIX Electronics Corporation. All rights reserved.

ASIX [ ASIX ELECTRONICS CORPORATION ]

ASIX [ ASIX ELECTRONICS CORPORATION ]