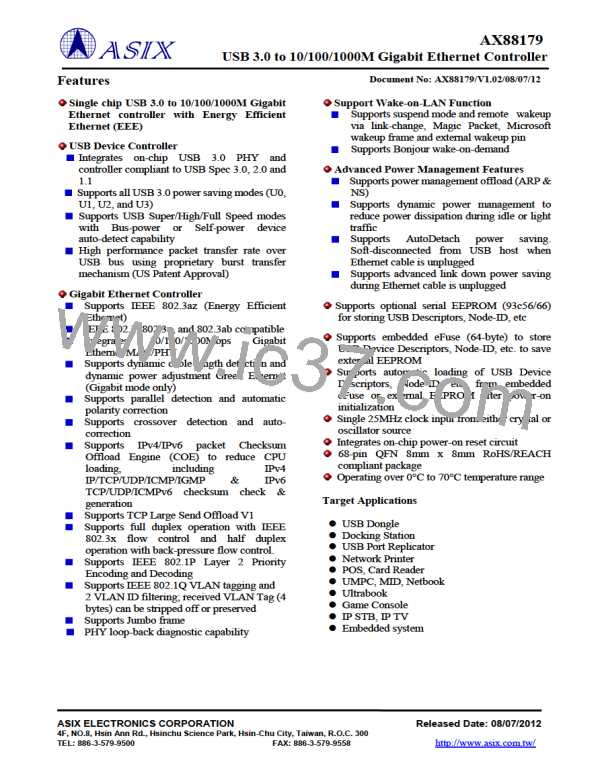

AX88179

USB 3.0 to 10/100/1000M Gigabit Ethernet Controller

3 Function Description

3.1 USB Core and Interfaces

The USB core and interfaces contains two USB 3.0 transceiver interfaces (PIPE/UTMI) and a USB3.0 Device Controller.

The USB 3.0 transceiver (or PHY) processes USB3.0/2.0/1.1 Physical layer signals. And, The USB3.0 Device Controller is

interfacing with USB 3.0 transceiver by PIPE/UTMI buses and it processes packets of Link layer and protocol layer. Also,

The USB 3.0 Device Controller contains Bulk IN and Bulk OUT buffers for handling Bulk transfer traffic and a FIFO for

Interrupt IN transfers.

The USB core and interfaces are used to communicate with a USB host controller and is compliant with USB specification

V3.0, V2.0, and V1.1.

3.2 Energy Efficient Ethernet (EEE)

It supports IEEE 802.3az also known as Energy Efficient Ethernet (EEE) at 10Mbps, 100Mbps and 1000Mbps. And also

supports EEE specified a negotiation method to enable link partner to determine whether EEE is supported and to select the

best set of parameters common to both device. It provides a protocol to coordinate transitions to/from a lower power

consumption level (Low Power Idle mode) based on link utilization. When no packets are being transmitted, the system

goes to Low Power Idle mode to save power. Once packets need to be transmitted, the system returns to normal mode, and

does this without changing the link status and without dropping/corrupting frames.

To save power, when the system is in Low Power Idle mode, most of the circuits are disabled; however, the transition time

to/from Low Power Idle mode is kept small enough to be transparent to upper layer protocols and applications.

3.3 10/100/1000M Ethernet PHY

The 10/100/1000M Ethernet PHY is compliant with 10Base-T, 100Base-TX, and 1000Base-T IEEE 802.3 standards. It

provides all the necessary physical layer functions to transmit and receive Ethernet packets over CAT 5 UTP cable or CAT

3 UTP (10Mbps only) cable. It uses state-of-the-art DSP technology and an Analog Front End (AFE) to enable high-speed

data transmission and reception over UTP cable. Functions such as Crossover Detection & Auto-Correction, polarity

correction, adaptive equalization, cross-talk cancellation, echo cancellation, timing recovery, and error correction are

implemented.

12

Copyright © 2011-2012 ASIX Electronics Corporation. All rights reserved.

ASIX [ ASIX ELECTRONICS CORPORATION ]

ASIX [ ASIX ELECTRONICS CORPORATION ]