QUAD GIGABIT ETHERNET TRANSCEIVER

S2066

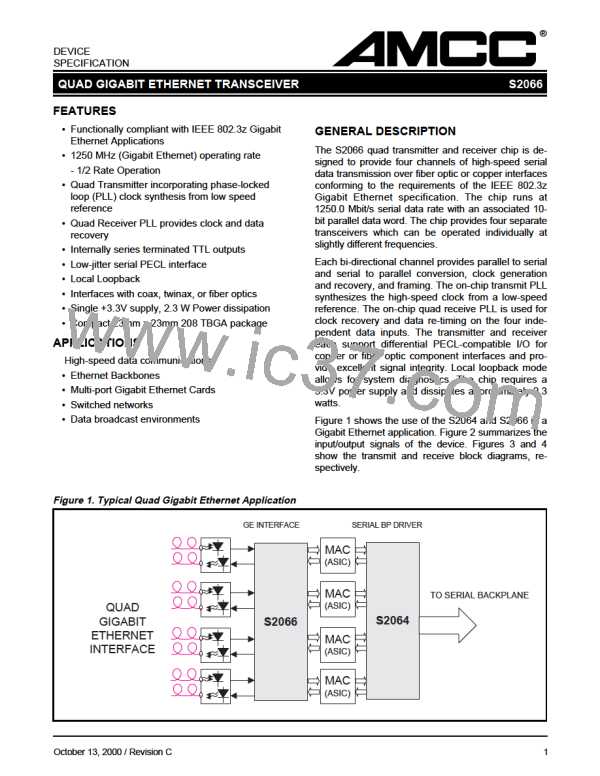

Figure 7. S2066 Pinout (Bottom View)

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

COM_

DETB

1

2

VDDA

DIGPWR DIGGND TTLGND TTLPWR DOUTA1

DOUTA9

DOUTA0

DOUTA8

DOUTA4

DOUTA3

DOUTA2

DOUTA7

DOUTA5

DOUTA6

RBC0A

RBC1A

DOUTB0 DOUTB2 DOUTB6 DOUTB7

COM_

RBC0B

RBC1B

COM_

DETA

VSSSUB DIGPWR

CMODE

DIGGND

VSSA

DIGGND TTLGND

DOUTB1 DOUTB3 DOUTB4 DOUTB8

DOUTC9 DOUTC1

DETC

3

PWR

VSS

RXAN

VDD

PWR

RXAP

GND

DIGPWR TTLGND

DOUTB9 TTLGND DOUTB5 TTLPWR DOUTC8 DIGGND DOUTC0 DOUTC4

TEST

MODE

4

DIGGND TTLPWR TTLPWR TTLGND TTLPWR DIGPWR TTLGND DIGGND TTLGND TTLGND DOUTC3

RBC0C

RBC1C

5

GND

RXBN

VDD

PWR

TTLPWR DOUTC2 DOUTC5

TTLGND DOUTC6 DOUTD9

COM_

DETD

6

VDDA

VSSSUB

RXCP

RXCN

GND

RXBP

VSS

7

VSSA

VSSA

PWR

VSS

GND

PWR

TTLPWR DOUTC7 DOUTD8 DOUTD1

TTLPWR TTLGND DOUTD0 DOUTD2

DIGPWR DOUTD4 DOUTD3 DOUTD5

8

VDDA

VSSSUB

VDD

9

PWR

10

11

12

13

14

15

16

17

GND

PWR

DIGGND DOUTD6

RBC1D

DINA0

DINA4

DINA5

DINB0

DINB5

DINB8

DINC1

RBC0D

DOUTD7

TBCA

VSS

PWR

RXDN

TMODE

VSS

RXDP

VSSA

RATE

CAP1

LPEN

GND

DINA2

DINA7

DINB1

DINB6

TBCC

DINC3

DINC8

DINA1

DINA6

TBCB

DINB4

DINB7

DINB9

DINC4

VDD

CLKSEL

VSSSUB

CAP2

VDDA

VSSSUB

VDD

DINA3

DINA8

DINA9

DINB2

DINB3

GND

GND

GND

GND

GND

GND

GND

TCLKO

DIGGND

DIND9

DIND4

DIND5

DIND6

DIND8

TBCD

DIND0

DIND2

DIND7

DINC5

DINC7

DIND1

DIND3

DINC0

DINC2

DINC6

DINC9

PECL

PWR

VSSA

PWR

TXAN

RESET

PECLGND

TXBP

PECL

PWR

VDDA

TXAP

GND

GND

TXCP

TXDP

PECLGND

TXBN

TXCN

TXDN

REFCLK DIGPWR

17

October 13, 2000 / Revision C

AMCC [ APPLIED MICRO CIRCUITS CORPORATION ]

AMCC [ APPLIED MICRO CIRCUITS CORPORATION ]