September 2005

rev 1.4

ASM5P23S08A

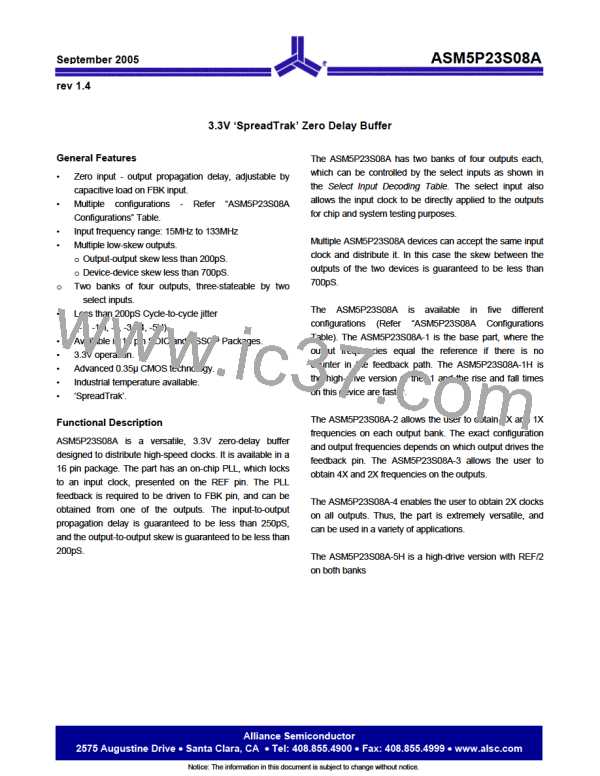

Block Diagram

ASM5P23S08A

FBK

/2

PLL

MUX

REF

/2

CLKA1

Extra Divider (-5H)

Extra Divider (-3, -4)

CLKA2

CLKA3

CLKA4

S2

S1

Select Input

Decoding

/2

CLKB1

CLKB2

CLKB3

CLKB4

Extra Divider (-2, -3)

Select Input Decoding for ASM5P23S08A

S2

0

S1

0

Clock A1 - A4

Three-state

Clock B1 - B4

Three-state

Output Source

PLL Shut-Down

PLL

Y

0

1

1

1

0

1

Driven

Driven1

Driven

Three-state

Driven

PLL

Reference

PLL

N

Y

N

Driven

ASM5P23S08A Configurations

Device

Feedback From

Bank A or Bank B

Bank A or Bank B

Bank A

Bank A Frequency

Reference

Bank B Frequency

ASM5P23S08A-1

ASM5P23S08A-1H

ASM5P23S08A-2

ASM5P23S08A-2

ASM5P23S08A-3

ASM5P23S08A-3

ASM5P23S08A-4

ASM5P23S08A-5H

Reference

Reference

Reference

Reference

Reference /2

Reference

Bank B

Bank A

Bank B

2 X Reference

2 X Reference

4 X Reference

2 X Reference

Reference /2

Reference or Reference2

2 X Reference

2 X Reference

Reference /2

Bank A or Bank B

Bank A or Bank B

Note:

1. Outputs are non- inverted on ASM5P23S08A-2 and ASM5P23S08A-3 in bypass mode, S2 = 1 and S1 = 0.

2. Output phase is indeterminant (0° or 180° from input clock). If phase integrity is required, use the ASM5P23S08A-2.

3.3V ‘SpreadTrak’ Zero Delay Buffer

2 of 18

Notice: The information in this document is subject to change without notice.

ALSC [ ALLIANCE SEMICONDUCTOR CORPORATION ]

ALSC [ ALLIANCE SEMICONDUCTOR CORPORATION ]