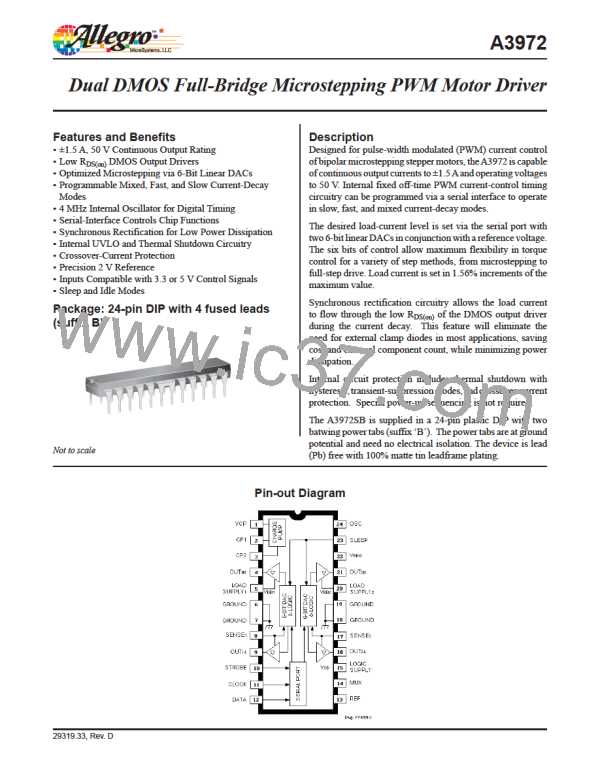

Dual DMOS Full-Bridge

Microstepping PWM Motor Driver

A3972

FUNCTIONAL DESCRIPTION (continued)

VREG. This internally generated supply voltage is used to run

the sink-side DMOS outputs. VREG is internally monitored and

in the case of a fault condition, the outputs of the device are

disabled. The VREG pin should be decoupled with a 0.22 μF

capacitor to ground.

Shutdown. In the event of a fault due to excessive junction

temperature, or low voltage on VCP or VREG, the outputs of the

device are disabled until the fault condition is removed. At

power up, or in the event of low VDD, the UVLO circuit disables

the drivers and resets the data in the serial port to zeros.

Current Regulation. The reference voltage can be set by ana-

log input to the REF terminal, or via the internal 2 V precision

reference. The choice of reference voltage and sense resistor set

the maximum trip current.

Synchronous Rectification. When a PWM off-cycle is

triggered, either by a bridge disable command or internal fixed

off-time cycle, the load current will recirculate according to

the decay mode selected by the control logic. The A3972SB

synchronous rectification feature will turn on the appropriate

MOSFET(s) during the current decay and effectively short out

the body diodes with the low rDS(on) driver. This will lower

power dissipation significantly and can eliminate the need for

external Schottky diodes for most applications.

ITRIPMAX = VREF/(Range x RS)

Microstepping current levels are set according to the following

equations:

ITRIP = VDAC/(Range x RS)

VDAC = [(1 + DAC) x VREF]/64

Four distinct modes of operation can be configured with the two

serial port control bits:

where DAC input code equals 1 to 63 and Range is 4 or 8 as

selected by Word 0, D18. Programming the DAC input code to

zero disables the bridge, and results in minimum load current.

1. Active Mode. Prevents reversal of load current by turning

off synchronous rectification when a zero current level is

detected.

PWM Timer Function. The PWM timer is programmable via

the serial port to provide fixed off-time PWM signals to the con-

trol block. In mixed-decay mode, the first portion of the off time

operates in fast decay, until the fast-decay time count is reached,

followed by slow decay for the rest of the fixed off-time period.

If the fast-decay time is set longer than the off-time, the device

effectively operates in fast-decay mode.

2. Passive Mode. Allows reversal of current but will turn

off the synchronous rectifier circuit if the load current inver-

sion ramps up to the current limit.

3. Disabled. MOSFET switching will not occur during load

recirculation. This setting would only be used with four

external clamp diodes per bridge.

Oscillator. The PWM timer is based on an oscillator input,

typically 4 MHz. The A3972SB can be configured to select ei-

ther a 4 MHz internal oscillator or, if more precision is required,

an external clock can be connected to the OSC terminal. If an

external clock is used, three internal divider choices are select-

4. Low Side Only. The low-side MOSFETs will switch on

during the off time to short out the current path through

the MOSFET body diode. With this setting, the high-side

MOSFETs will not synchronously rectify so four external

diodes from output to supply are recommended. This mode

is intended for use with high-power applications where it

is desired to save the expense of two external diodes per

bridge. In this mode, the sink-side MOSFETs are chopped

during the PWM off time. In all other cases, the source-side

MOSFETs are chopped in response to a PWM off com-

mand.

able via the serial port to allow flexibility in choosing fOSC

,

based on available system clocks. If the internal oscillator op-

tion is used, the absolute accuracy is dependent on the process

variation of resistance and capacitance. A precision resistor can

be connected from the OSC terminal to VDD to further improve

the tolerance. The frequency will be:

fOSC = 204 x 109/ROSC

If the internal oscillator is used without the external resistor, the

OSC terminal should be connected to ground.

Sleep Mode. The input terminal SLEEP is dedicated to putting

the device into a minimum current draw mode. When pulled

low, the serial port will be reset to all zeros and all circuits will

be disabled.

continued next page ...

Allegro MicroSystems, LLC

115 Northeast Cutoff

8

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

ALLEGRO [ ALLEGRO MICROSYSTEMS ]

ALLEGRO [ ALLEGRO MICROSYSTEMS ]