Dual DMOS Full-Bridge

Microstepping PWM Motor Driver

A3972

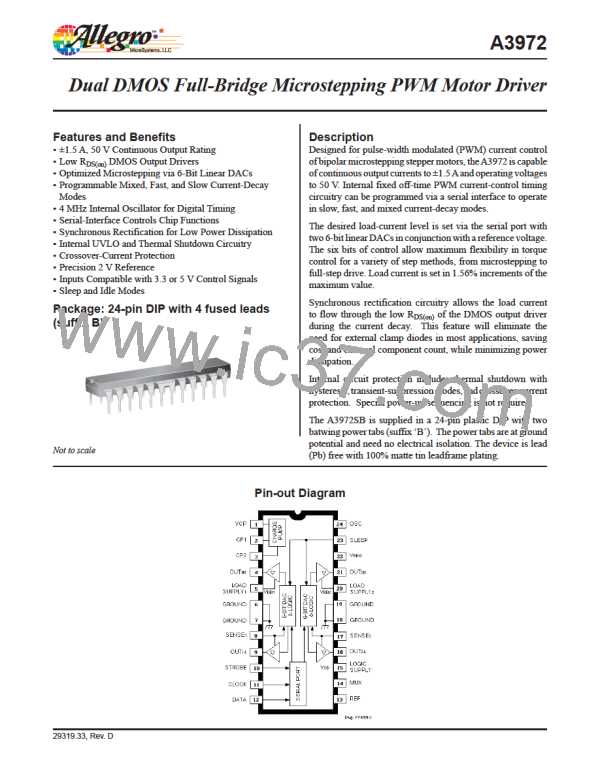

FUNCTIONAL BLOCK DIAGRAM

0.22 MF

0.22 MF

V

CP2

CP1

REG

22

3

2

LOGIC

SUPPLY

LOAD

SUPPLY

2 V

V

V

CP

UVLO AND

FAULT

DETECT

REGULATOR

BANDGAP

1

5

CHARGE PUMP

DMOS H-BRIDGE

15

V

DD

0.22 MF

BB1

14

MUX

6-BIT

LINEAR

DAC

SENSE

1

V

CP

+

-

OUT

1A

6

9

4

PROGRAMMABLE

PWM TIMER

OUT

1B

OSCILATOR

OSC

24

FIXED-OFF

BLANK

MIXED DECAY

OSC SELECT/

DIVIDER

SENSE

1

8

11

12

10

CLOCK

DATA

CONTROL

LOGIC

SERIAL

PORT

GATE

DRIVE

0.1 MF

DMOS H-BRIDGE

20

PHASE 1/2

SYNC. RECT. MODE

SYNC. RECT. DISABLE

MODE 1/2

V

STROBE

BB2

23

SLEEP

OUT

2A

16

21

PROGRAMMABLE

PWM TIMER

OUT

2B

2 V

FIXED-OFF

BLANK

MIXED DECAY

6

BUFFER

REF

13

+

-

SENSE

6-BIT

LINEAR

DAC

2

17

0.1 MF

6

7

18 19

GROUND

Dwg. FP-050-1

Allegro MicroSystems, LLC

115 Northeast Cutoff

3

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Copyright © 2000, Allegro MicroSystems, LLC

ALLEGRO [ ALLEGRO MICROSYSTEMS ]

ALLEGRO [ ALLEGRO MICROSYSTEMS ]