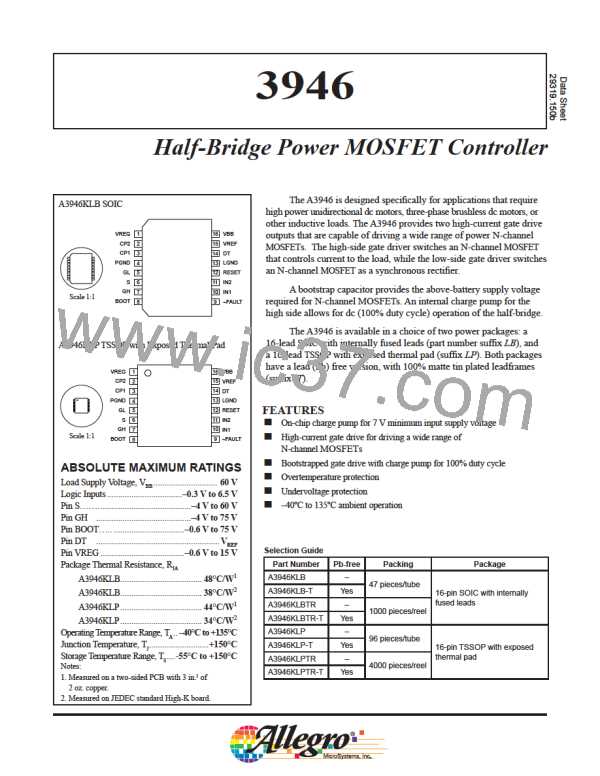

3946

Half-Bridge Power MOSFET Controller

Functional Block Diagram

+VBAT

C1

C2

0.47 uF, X7R

V rated to VBAT

0.47 uF, X7R

V rated to VBAT

P

VBB

CP2

CP1

VREF

VREG

BOOT

Charge

Pump

+5 Vref

L

CREG

0.1 uF

X7R

10 V

ILIM

10

kΩ

P

L

P

Charge

Pump

~FAULT

Protection

VREG Undervoltage

Overtemperature

UVLOBOOT

Bootstrap

UVLO

CBOOT

L

VREF

RGATE

GH

High Side

Driver

P

DT

Turn-On

Delay

RDEAD

IN1

Control

Logic

S

L

VREG

L

L

RGATE

IN2

GL

Low Side

Driver

PGND

LGND

L

P

RESET

L

P

Control Logic Table

IN1

X

0

IN2

X

0

DT Pin

X

RESET

GH

Z

GL

Z

Function

0

1

1

1

1

1

1

1

1

Sleep mode

R

DEAD - LGND

L

H

L

Low-side FET ON following dead time

0

1

RDEAD - LGND

RDEAD - LGND

RDEAD - LGND

VREF

L

All OFF

All OFF

1

0

L

L

1

1

H

L

L

High-side FET ON following dead time

All OFF

0

0

L

0

1

VREF

L

H

L

Low-side FET ON

1

0

VREF

H

H

High-side FET ON

1

1

VREF

H

CAUTION: High-side and low-side FETs ON

2

www.allegromicro.com

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

ALLEGRO [ ALLEGRO MICROSYSTEMS ]

ALLEGRO [ ALLEGRO MICROSYSTEMS ]