[ASAHI KASEI]

[AK7740ET]

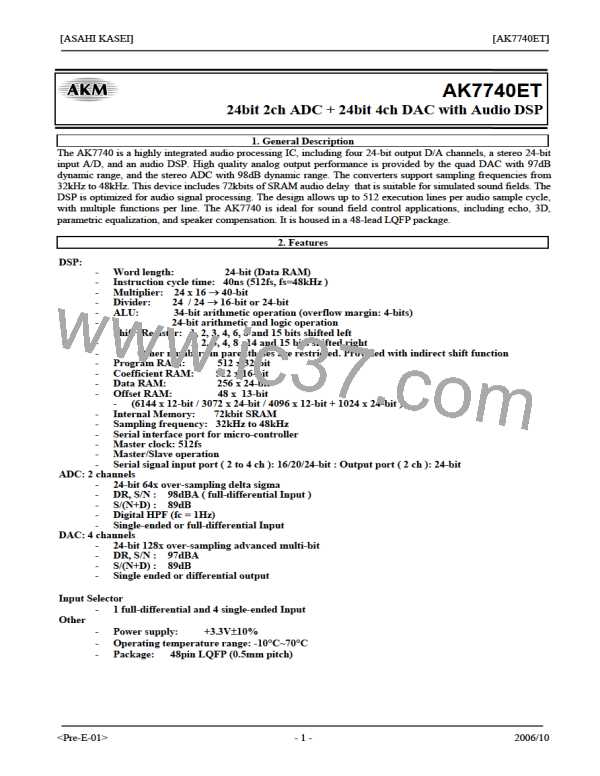

7-1-c) Coefficient RAM write (during reset phase)

The data comprising a set of five bytes is used to perform coefficient RAM write operations (during reset phase).

When all data has been transferred, the RDY terminal goes "H". Upon completion the CRAM write, RDY goes to

"H" to allow the next data to be inputted. When writing data of continuous addresses, input the data as they are (no

command code or address is required). To write discontinuous data, shift the RQ terminal from "H" to "L". Then

input the command code, address and data in that order.

Data transfer procedure

c Command code A0h ( 1 0 1 0 0 0 0 0 )

d Address upper

e Address lower

f Data

( 0 0 0 0 0 0 0 A8)

(A7 . . . . . . . A0)

(D15 . . . . . . D8)

(D7 . . . . . . D0)

g Data

S_RESET

RQ

SCLK

SI

10100000 0000000 A8

A7****A1A0

D15****D0

D15****D0

RDY

SO

Input of continuous address data into CRAM

S_RESET

RQ

SCLK

10100000 0000000 A8 A7***A1A0 D15****D0

D15*

A7***A1A0

10100000 0000000 A8

SI

RDY

SO

Input of discontinuous address data into CRAM

<Pre-E-01>

- 32 -

2006/10

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]