[ASAHI KASEI]

[AK7740ET]

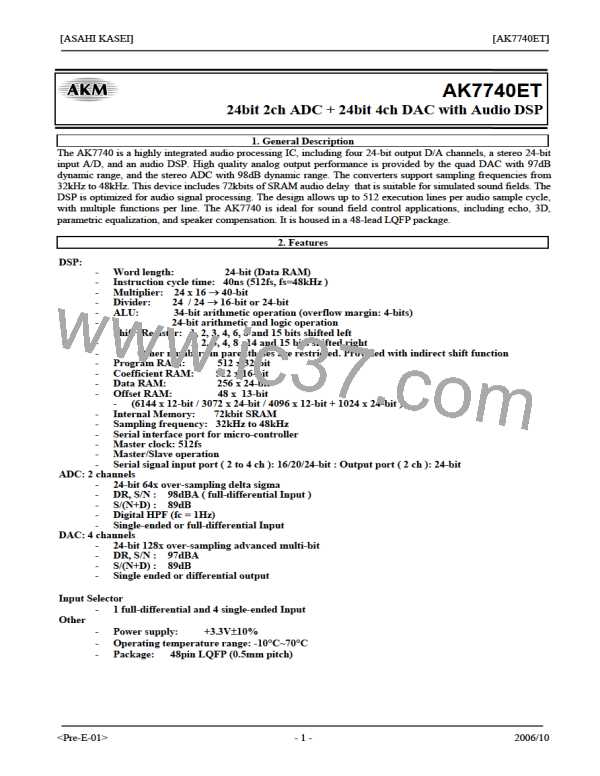

7-1-e) External conditional jump code write (during reset phase)

The data comprising a set of two bytes is used to perform an external conditional jump code write operation. Input the

data during either the reset or operation phase, and the input data are set to the specified register at the leading edge of

the LRCLK. When all data bits have been transferred, the RDY terminal goes to "L". Upon completion of writing, it

goes to "H". A jump command will be executed if there is any one agreement between "1" of each bit of external

condition code eight bits (soft set), plus one bit (hard set) at the external input terminal JX and "1" of each bit of the

IFCON field. The data during the reset phase can be written only before release of the reset, after all data has been

transferred. RQ Transition from "L" to "H" in the write operation during the reset phase must be executed after

three LRCLK in slave mode or one LRCLK in master mode, respectively, from the trailing edge of LRCLK after

release of the reset. Then RDY goes to "H" after capturing the rise of the next LRCLK. Write operations from the

microcontroller are disabled until RDY goes to "H". The IFCON field provides external conditions written on the

program. It resets to 00h by INIT_RESET =”L”, however, it remains previous condition even S_RESET =”L”.

Note: LRCLK phase is inverted in the I2S-compatible mode.

7

0 JX

External condition code

Ç

Check if there is any one agreement between the bit specified in IFCON and

"1" in the external condition code

16

IFCON field

È

8

Data transfer procedure

c Command code

d Code data

C4h ( 1 1 0 0 0 1 0 0)

(D7 . . . . . D0)

Max 1LRCLK

S_RESET

SCLK

SI

11000100 D7 **** D0

SO

RQ

L ch R ch

LRCLK

2LRCLK(max)

Timing for external conditional jump write operation (during reset phase)

RDY

<Pre-E-01>

- 34 -

2006/10

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]