AD9807/AD9805

P IN CO NFIGURATIO N

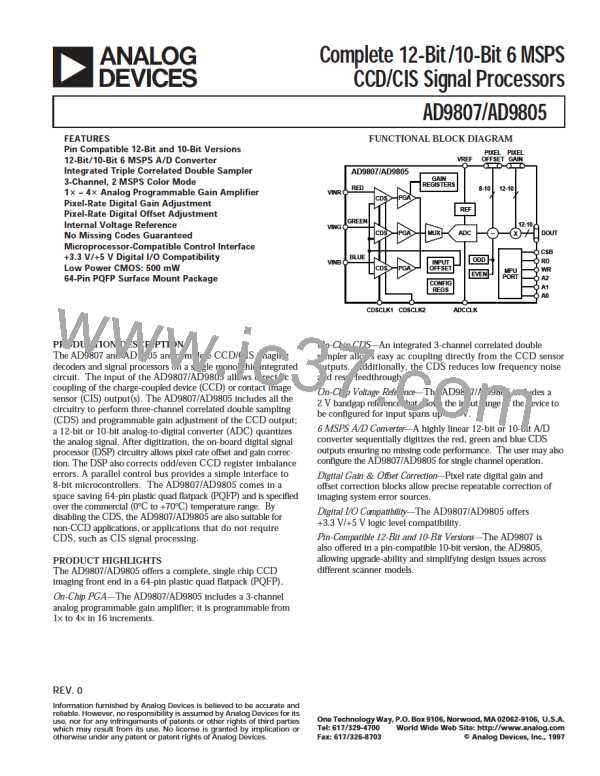

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

1

2

AVDD

AVSS

CAPT

CAPT

CAPB

CAPB

VREF

48

47

A0

PIN 1

IDENTIFIER

DOUT<11>

3

46 DOUT<10>

DOUT<9>

4

45

5

44 DOUT<8>

6

43 DOUT<7>/MPU<7>

7

DOUT<6>/MPU<6>

DRVDD

42

AD9807

8

CML

VINR

41

40

TOP VIEW

9

DRVSS

(Not to Scale)

10

AVSS

39 DOUT<5>/MPU<5>

VING 11

38

DOUT<4>/MPU<4>

12

13

14

AVSS

VINB

AVSS

37

36

DOUT<3>/MPU<3>

DOUT<2>/MPU<2>

35 DOUT<1>/MPU<1>

AVDD 15

16

34

DOUT<0>/MPU<0>

OEB

STRTLN

33

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

P IN D ESCRIP TIO NS

P in No.

P in Nam e

Type

D escription

1, 15

2, 10, 12, 14

AVDD

AVSS

P

P

+5 V Analog Supply.

Analog Ground.

3, 4

5, 6

7

8

CAPT

CAPB

VREF

CML

AO

AO

AO

AO

AI

Reference Decoupling. See Figure 22.

Reference Decoupling.

Internal Reference Output. Decouple with 10 µF + 0.1 µF.

Internal Bias Voltage. Decouple with 0.1 µF.

Analog Input, Red.

9

VINR

11

VING

AI

Analog Input, Green.

13

VINB

AI

Analog Input, Blue.

16

17

18

19

28, 52

29, 51

20

21–26

27

30

31

32

33

ST RT LN

CDSCLK1

CDSCLK2

ADCCLK

DVSS

DI

DI

DI

DI

P

ST RT LN. Indicates beginning of scan line.

CDS Reset Clock Pulse Input.

CDS Data Clock Pulse Input.

A/D Sample Clock Input.

Digital Ground.

+5 V Digital Supply.

Pixel Rate Offset Coefficient Inputs. Most Significant Bit.

Pixel Rate Offset Coefficient Inputs.

Pixel Rate Offset Coefficient Inputs. Least Significant Bit.

Chip Select. Active Low.

Read Strobe. Active Low.

Write Strobe. Active Low.

DVDD

P

OFFSET <7>

OFFSET <6:1>

OFFSET <0>

CSB

RDB

WRB

DI

DI

DI

DI

DI

DI

DI

DIO

DIO

P

OEB

Output Enable. Active Low.

34

DOUT <0>/MPU<0>

DOUT <1:6>/MPU<1:6>

DRVSS

Data Output LSB/Register Input LSB

Data Outputs/Register Inputs.

Digital Driver Ground

35–39, 42

40

41

DRVDD

P

Digital Driver Supply

43

44–46

47

48, 49, 50

53

54–63

64

DOUT <7>/MPU<7>

DOUT <8:10>

DOUT <11>

A0, A1, A2

GAIN<0>

DIO

DO

DO

DI

DI

DI

DI

Data Output/Register Input MSB.

Data Outputs.

Data Output MSB.

Register Select Pins.

Pixel Rate Gain Coefficient Input. LSB.

Pixel Rate Gain Coefficient Inputs.

Pixel Rate Gain Coefficient Input. MSB.

GAIN<1:10>

GAIN<11>

T YPE: AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; DIO = Digital Input/Output; P = Power.

REV. 0

–5–

ADI [ ADI ]

ADI [ ADI ]