AD9807/AD9805

PIXEL n

PIXEL n+1

PIXEL n+2

RIN, GIN, BIN

R, G, B

R, G, B

R, G, B

CDSCLK1

ADCCLK

R

G

B

R

G

B

R

G

B

DATA<11:0>

R (n–2)

G (n–2)

B (n–2)

R (n–1)

G (n–1)

B (n–1)

R (n)

GAIN<n:0>

GAIN<m:0>

R (n)

G (n)

B (n)

R (n+1)

G (n+1)

B (n+1)

R (n+2)

G (n+2)

B (n+2)

R (n+3)

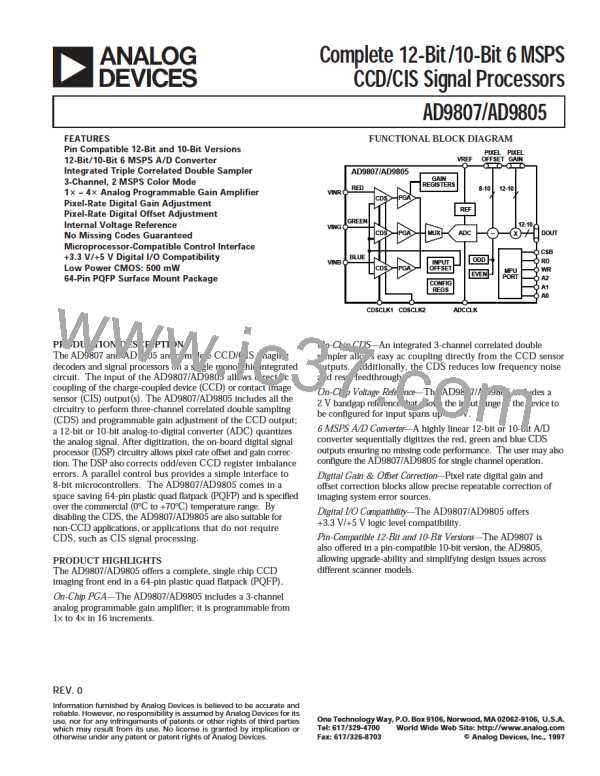

Figure 13. DOUT Latency, 3-Channel SHA Mode

PIXEL n

PIXEL n+1

PIXEL n+2

RIN, GIN, BIN

CDSCLK1

CDSCLK2

ADCCLK

D (n–8)

D (n–7)

D (n–6)

D (n–5)

D (n–4)

DATA<11:0>

GAIN<n:0>

OFFSET<m:0>

G (n+1)

G (n+2)

G (n)

G (n+3)

Figure 14. DOUT Latency, 1-Channel CDS Mode

PIXEL n

PIXEL n+1

PIXEL n+2

RIN, GIN, BIN

CDSCLK1

ADCCLK

DATA<11:0>

D (n–7)

D (n–6)

D (n–5)

D (n–4)

GAIN<n:0>

OFFSET<m:0>

G (n)

G (n+1)

G (n+2)

G (n+3)

Figure 15. DOUT Latency, 1-Channel SHA Mode

REV. 0

–16–

ADI [ ADI ]

ADI [ ADI ]