Data Sheet

AD9364

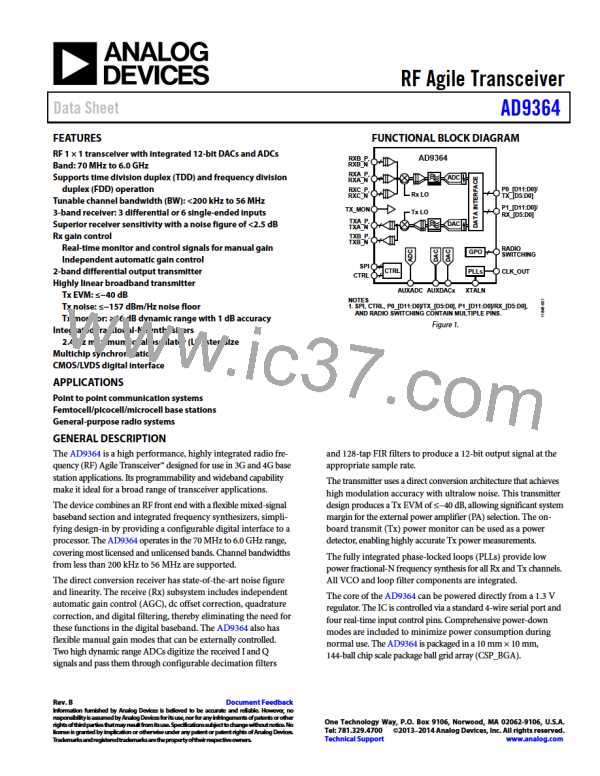

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

2

3

4

5

6

7

8

9

10

11

12

VDDA1P3_ VDDA1P3_ VDDA1P3_ VDDA1P3_ VDDA1P1_

TX_EXT_

LO_IN

VSSA

VSSA

NC

VSSA

VSSA

VSSA

A

B

C

D

E

F

RX_TX

RX_TX

RX_TX

RX_TX

TX_VCO

VDDA1P3_

TX_VCO_

LDO

VDDA1P3_

TX_LO

TX_VCO_

LDO_OUT

VSSA

VSSA

VSSA

VSSA

VSSA

VSSA

VSSA

AUXDAC1

AUXDAC2

GPO_3

GPO_2

GPO_1

GPO_0

VDD_GPO

VSSA

VSSA

VSSD

TEST/

ENABLE

CTRL_IN0

CTRL_IN1

CTRL_IN2

VSSA

VSSA

VSSA

VSSA

VSSA

VDDA1P3_ VDDA1P3_

RX_RF

P0_D9/

P0_D7/

P0_D5/

P0_D3/

P0_D1/

CTRL_OUT0 CTRL_IN3

RX_TX

TX_D4_P

TX_D3_P

TX_D2_P

TX_D1_P

TX_D0_P

VDDA1P3_

TX_LO_

BUFFER

VDDA1P3_

RX_LO

P0_D11/

P0_D8/

P0_D6/

P0_D4/

P0_D2/

P0_D0/

TX_D0_N

CTRL_OUT1 CTRL_OUT2 CTRL_OUT3

CTRL_OUT6 CTRL_OUT5 CTRL_OUT4

TX_D5_P

TX_D4_N

TX_D3_N

TX_D2_N

TX_D1_N

VDDA1P3_

RX_VCO_

LDO

P0_D10/

TX_D5_N

VDDD1P3_

DIG

VSSA

VSSD

VSSD

FB_CLK_P

FB_CLK_N

VSSD

VSSD

RX_EXT_

LO_IN

RX_VCO_

LDO_OUT

VDDA1P1_

RX_VCO

RX_

FRAME_N

RX_

FRAME_P

TX_

FRAME_P

DATA_

CLK_P

CTRL_OUT7

TXNRX

EN_AGC

SYNC_IN

SPI_CLK

RESETB

AUXADC

TX_MON

ENABLE

VSSA

VSSD

G

H

J

P1_D11/

RX_D5_P

TX_

FRAME_N

DATA_

CLK_N

VDD_

INTERFACE

RXB_P

RXB_N

RXC_P

RXC_N

RXA_P

VSSA

VSSA

VSSA

VSSA

RXA_N

VSSA

VSSD

VDDA1P3_

RX_SYNTH

P1_D10/

P1_D9/

P1_D7/

P1_D5/

P1_D3/

P1_D1/

RX_D0_P

SPI_DI

CLK_OUT

SPI_ENB

SPI_DO

VSSA

RX_D5_N

RX_D4_P

RX_D3_P

RX_D2_P

RX_D1_P

VDDA1P3_ VDDA1P3_

TX_SYNTH

P1_D8/

P1_D6/

P1_D4/

P1_D2/

P1_D0/

K

L

VSSD

VSSA

BB

RX_D4_N

RX_D3_N

RX_D2_N

RX_D1_N

RX_D0_N

VSSA

RBIAS

VSSA

VSSA

VSSA

VSSA

VSSA

M

NC

VSSA

TXA_P

TXA_N

TXB_P

TXB_N

XTALP

XTALN

ANALOG I/O

DIGITAL I/O

DC POWER

GROUND

NO CONNECT

Figure 2. Pin Configuration, Top View

Table 13. Pin Function Descriptions

Pin No.

Type1 Mnemonic

Description

A1, A2, A4 to

A6, B1, B2,

I

VSSA

Analog Ground. Tie these pins directly to the VSSD digital ground on the printed

circuit board (one ground plane).

B12, C1, C2,

C7 to C12, D1,

E1, F1, F3, H2,

H3, H6, J2, K2,

L2, L3, L7 to

L12, M4, M6

A3, M3

A7 to A10, D3

A11

NC

NC

No Connect. Do not connect to these pins.

1.3 V Supply Input.

Transmit VCO Supply Input. Connect to B11.

External Transmit Local Oscillator (LO) Input. When this pin is unused, tie it to

ground.

I

I

I

VDDA1P3_RX_TX

VDDA1P1_TX_VCO

TX_EXT_LO_IN

A12

B3

B4 to B7

B8

O

O

I

AUXDAC1

GPO_3 to GPO_0

VDD_GPO

Auxiliary DAC 1 Output.

3.3 V Capable General-Purpose Outputs.

2.5 V to 3.3 V Supply for the Auxiliary DAC and General-Purpose Output Pins.

When the VDD_GPO supply is not used, this supply must be set to 1.3 V.

B9

I

VDDA1P3_TX_LO

Transmit LO 1.3 V Supply Input.

B10

B11

I

O

VDDA1P3_TX_VCO_LDO

TX_VCO_LDO_OUT

Transmit VCO LDO 1.3 V Supply Input. Connect to B9.

Transmit VCO LDO Output. Connect B11 to A11 and a 1 μF bypass capacitor in

series with a 1 Ω resistor to ground.

C3

C4

O

I

AUXDAC2

TEST/ENABLE

Auxiliary DAC 2 Output.

Test Input. Ground this pin for normal operation.

Rev. B | Page 11 of 32

ADI [ ADI ]

ADI [ ADI ]