NT5DS32M4AT

NT5DS16M8AT

128Mb Double Data Rate SDRAM

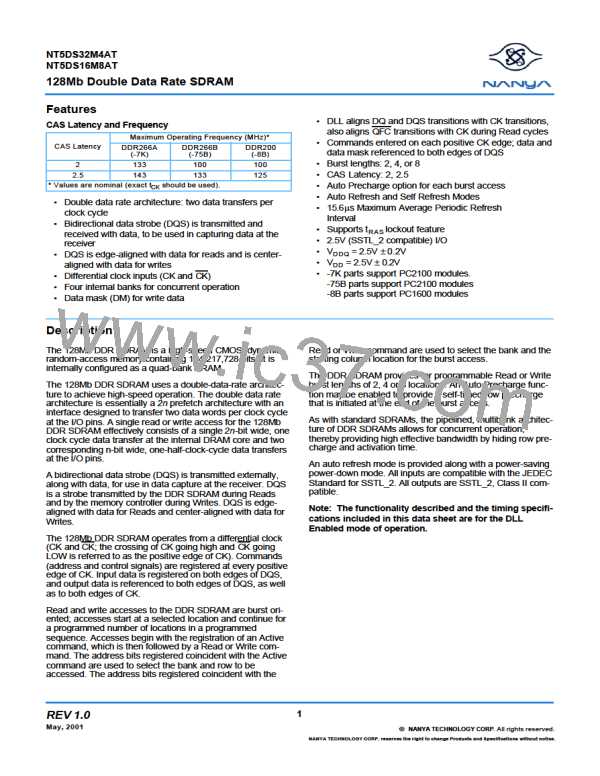

Write to Read: Non-Interrupting (CAS Latency = 2; Burst Length = 4)

Maximum DQSS

T1

T2

T3

T4

T5

T6

CK

CK

Write

NOP

NOP

NOP

Read

NOP

Command

t

WTR

BAa, COL b

BAa, COL n

Address

CL = 2

t

(max)

DQSS

DQS

DQ

DI a-b

DM

Minimum DQSS

T1

T2

T3

T4

T5

T6

CK

CK

Write

NOP

NOP

NOP

Read

NOP

Command

t

WTR

BAa, COL b

BAa, COL n

Address

CL = 2

t

(min)

DQSS

DQS

DQ

DI a-b

DM

DI a-b = data in for bank a, column b.

3 subsequent elements of data in are applied in the programmed order following DI a-b.

A non-interrupted burst is shown.

t

is referenced from the first positive CK edge after the last data in pair.

WTR

A10 is Low with the Write command (Auto Precharge is disabled).

The Read and Write commands may be to any bank.

Don’ t Care

35

REV 1.0

May, 2001

©

NANYA TECHNOLOGY CORP. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

ETC [ ETC ]

ETC [ ETC ]