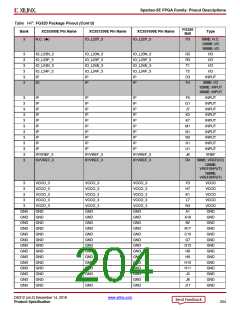

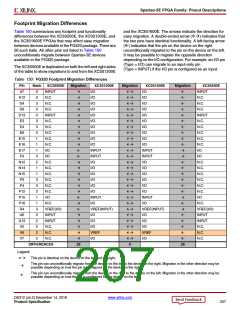

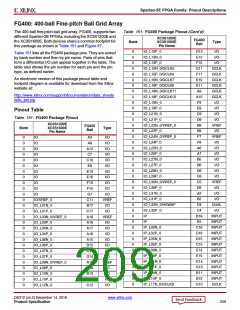

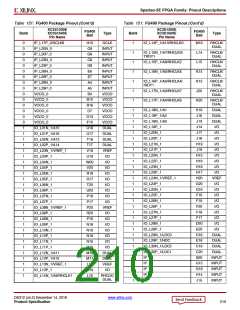

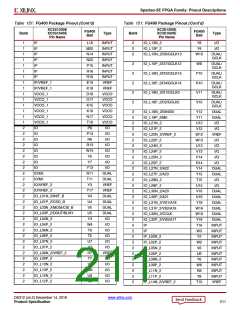

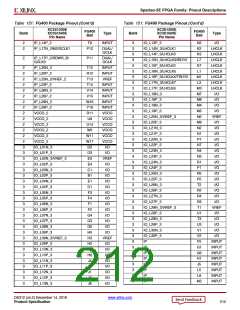

Spartan-3E FPGA Family: Pinout Descriptions

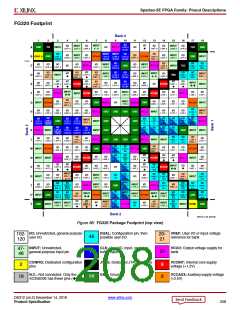

FG320 Footprint

X-Ref Target - Figure 86

Bank 0

1

2

3

4

5

6

7

8

9

10

11

I/O

12

13

14

15

16

17

18

I/O

L12N_0

GCLK7

I/O

INPUT

I/O

L24P_0

INPUT

L22P_0

I/O

L20N_0

I/O

L05P_0

I/O

L04N_0

INPUT

L02N_0

I/O

L01N_0

VCCO_0

GND

TDI

INPUT

I/O

TCK

GND

A

B

C

D

E

F

I/O

L25N_0

HSWAP

INPUT INPUT

I/O

L12P_0

GCLK6

I/O

L05N_0

VREF_0

I/O

INPUT

I/O

I/O

I/O

INPUT

I/O

PROG_B

VCCAUX

VCCAUX

GND

GND

INPUT

L13P_0

GCLK8

L13N_0

GCLK9

L24N_0

L22N_0

L20P_0

VREF_0

L04P_0

L02P_0

L01P_0

I/O

L14P_0

GCLK10

I/O

L03N_0

VREF_0

I/O

L24N_1

LDC2

I/O

L24P_1

LDC1

I/O

L01P_3

I/O

L01N_3

I/O

L25P_0

I/O

L23P_0

I/O

L18P_0

INPUT

L16P_0

I/O

L09P_0

INPUT

L07P_0

VCCO_0

VCCO_0

I/O

GND

INPUT

TMS

TDO

I/O

L21P_0

I/O

L02N_3

VREF_3

I/O

L23N_0

VREF_0

I/O

L18N_0

VREF_0

I/O

L14N_0

GCLK11

I/O

L11P_0

GCLK4

I/O

L23N_1

LDC0

I/O

L23P_1

HDC

INPUT

I/O

I/O

L02P_3

INPUT

L16N_0

I/O

L09N_0

INPUT

L07N_0

I/O

L03P_0

INPUT

VREF_1

INPUT

I/O

L04N_3

I/O

L04P_3

I/O

L21N_0

I/O

L22P_1

I/O

L22N_1

I/O

L19N_0

VREF_0

I/O

L11N_0

GCLK5

INPUT

I/O

L03N_3

I/O

L03P_3

I/O

L17P_0

I/O

L15P_0

I/O

L08P_0

I/O

L06N_0

VCCINT

I/O

VCCINT

INPUT

INPUT

I/O

L05P_3

I/O

L05N_3

I/O

L19P_0

I/O

L17N_0

I/O

L15N_0

INPUT

L10P_0

I/O

L08N_0

I/O

L06P_0

I/O

L21N_1

I/O

L21P_1

I/O

L19N_1

I/O

L19P_1

VCCO_3

VCCO_1

INPUT VCCINT

VCCINT

I/O

L06N_3

VREF_3

I/O

I/O

I/O

INPUT

I/O

I/O

I/O

I/O

VCCAUX

VCCO_0

VCCO_0

VCCAUX

INPUT

GND

I/O

GND

INPUT

G

H

J

L06P_3

L07N_3

L07P_3

L10N_0

L20N_1

L20P_1

L18P_1

L18N_1

I/O

L16N_1

A0

I/O

L10N_3

I/O

L10P_3

I/O

L09N_3

I/O

L09P_3

I/O

L08N_3

I/O

L08P_3

I/O

L17P_1

I/O

L17N_1

I/O

L16P_1

INPUT

VREF_1

VCCO_3

VCCO_1

GND

GND

GND

GND

GND

GND

INPUT

I/O

L13P_1

A6

RHCLK4

IRDY1

I/O

L12N_3

LHCLK3

IRDY2

I/O

I/O

I/O

I/O

L12P_3

LHCLK2

I/O

L11N_3

LHCLK1 LHCLK0

I/O

L11P_3

I/O

L15P_1

A2

I/O

L15N_1

A1

INPUT

VREF_3

L14N_1

A3

L14P_1

A4

L13N_1

A5

VCCO_1

GND

I/O

L13P_3

LHCLK4

TRDY2

INPUT

INPUT

VCCO_3

GND

RHCLK7 RHCLK6 RHCLK5

I/O

I/O

I/O

I/O

I/O

L13N_3

I/O

L14N_3

I/O

L14P_3

L12N_1

L11N_1

A9

L11P_1

A10

L12P_1

VCCO_3

INPUT

GND

GND

A7

GND

INPUT INPUT

K

L

A8

RHCLK3

TRDY1

LHCLK5 LHCLK7 LHCLK6

RHCLK1 RHCLK0

RHCLK2

I/O

L17N_3

VREF_3

I/O

L09N_1

A11

I/O

L09P_1

A12

I/O

I/O

L15P_3

I/O

L15N_3

I/O

L16P_3

I/O

L16N_3

I/O

L17P_3

I/O

VCCO_1

GND

GND

I/O

GND

GND

INPUT INPUT

L10N_1

L10P_1

VREF_1

I/O

L16P_2

M0

I/O

I/O

L18N_3

I/O

L18P_3

I/O

L19P_3

I/O

L19N_3

I/O

I/O

L07P_1

I/O

L07N_1

I/O

L08N_1

L12N_2

D6

VCCAUX

VCCO_2

VCCO_2

VCCAUX

INPUT

GND

L05N_1

L05P_1

VREF_1

M

N

P

R

T

GCLK13

I/O

L21P_2

I/O

L04N_1

I/O

L04P_1

I/O

I/O

I/O

L20P_3

I/O

L20N_3

I/O

L07P_2

I/O

L09N_2

I/O

L18N_2

I/O

INPUT

L12P_2

D7

L16N_2

DIN

VCCO_3

VCCO_1

INPUT INPUT

VCCINT

VCCINT

L08P_1

GCLK12

D0

I/O

L22P_3

I/O

L22N_3

I/O

L21N_2

I/O

I/O

L22P_2

A23

INPUT

I/O

I/O

L21N_3

I/O

L21P_3

I/O

L05N_2

I/O

L07N_2

I/O

L09P_2

I/O

L18P_2

I/O

L06P_1

I/O

L06N_1

L15N_2

D1

VCCINT

I/O

VCCINT

GCLK3

INPUT

VREF_3

I/O

I/O

L22N_2

A22

I/O

L24N_2

A20

I/O

L03N_1

VREF_1

I/O

L02P_1

A14

I/O

L23N_3

I/O

L23P_3

I/O

L04P_2

I/O

L05P_2

INPUT

L08N_2

I/O

L10P_2

I/O

D5

I/O

L20N_2

I/O

L03P_1

L15P_2

D2

INPUT

I/O

INPUT

GCLK2

INPUT

I/O

I/O

I/O

L01N_2

INIT_B

I/O

L24P_2

A21

I/O

L01N_1

A15

I/O

L02N_1

A13

I/O

L24N_3

I/O

L24P_3

I/O

L04N_2

INPUT

L08P_2

I/O

L10N_2

INPUT

L17P_2

I/O

L20P_2

I/O

VREF_2

L03N_2

MOSI

L14N_2

L26P_2

VS0

VCCO_2

VCCO_2

GND

I/O

M2

CSI_B

GCLK1

A17

I/O

INPUT

I/O

I/O

L01P_2

CSO_B

I/O

L26N_2

CCLK

I/O

L01P_1

A16

INPUT

INPUT

I/O

VREF_2

INPUT

L11P_2

INPUT

INPUT

L23N_2

L03P_2

DOUT

BUSY

L13P_2

L14P_2

L25N_2

VS1

VCCAUX

VCCAUX

INPUT

GND

GND

GND

U

V

D4

RDWR_B L17N_2

GCLK0

GCLK14

A18

I/O

I/O

L06P_2

I/O

I/O

INPUT

L11N_2

VREF_2

I/O

L19N_2

VREF_2

I/O

INPUT INPUT

L02N_2 L02P_2

I/O

M1

I/O

L19P_2

INPUT

L23P_2

L06N_2

L13N_2

D3

L25P_2

VS2

VCCO_2

INPUT

INPUT DONE

GND

VREF_2

GCLK15

A19

Bank 2

DS312-4_06_022106

Figure 86: FG320 Package Footprint (top view)

I/O: Unrestricted, general-purpose

DUAL: Configuration pin, then

VREF: User I/O or input voltage

102-

120

20-

21

46

16

user I/O

possible user-I/O

reference for bank

INPUT: Unrestricted,

general-purpose input pin

CLK: User I/O, input, or global

buffer input

VCCO: Output voltage supply for

bank

47-

48

20

CONFIG: Dedicated configuration

JTAG: Dedicated JTAG port pins

GND: Ground

VCCINT: Internal core supply

2

4

8

8

pins

voltage (+1.2V)

N.C.: Not connected. Only the

XC3S500E has these pins ().

VCCAUX: Auxiliary supply voltage

(+2.5V)

18

28

DS312 (v4.2) December 14, 2018

www.xilinx.com

Product Specification

208

XILINX [ XILINX, INC ]

XILINX [ XILINX, INC ]