R

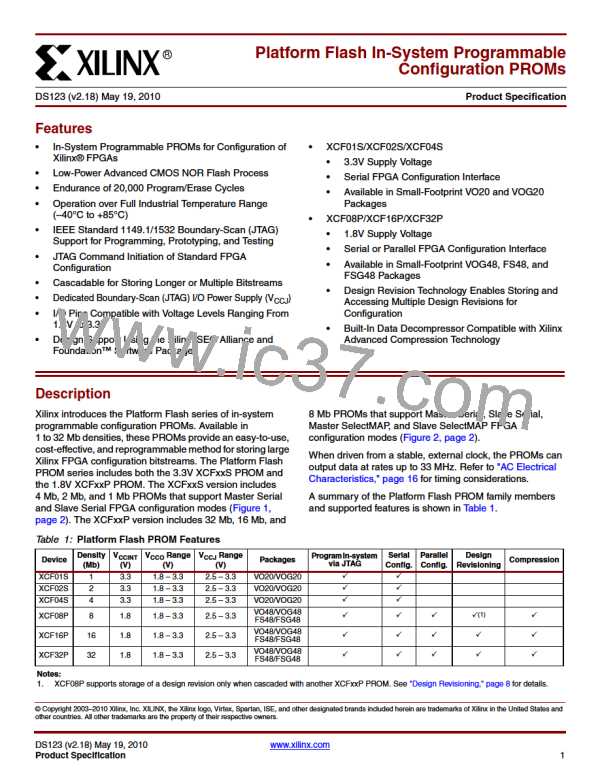

Platform Flash In-System Programmable Configuration PROMs

Platform Flash PROM TAP Characteristics

The Platform Flash PROM family performs both in-system

programming and IEEE 1149.1 Boundary-Scan (JTAG) testing

via a single 4-wire Test Access Port (TAP). This simplifies

system designs and allows standard Automatic Test

Equipment to perform both functions. The AC characteristics

of the Platform Flash PROM TAP are described as follows.

TAP Timing

Figure 4 shows the timing relationships of the TAP signals.

These TAP timing characteristics are identical for both

Boundary-Scan and ISP operations.

X-Ref Target - Figure 4

T

CKMIN

TCK

T

MSS

T

MSH

TMS

T

T

DIS

DIH

TDI

T

DOV

TDO

DS123_04_031808

Figure 4: Test Access Port Timing

TAP AC Parameters

Table 9 shows the timing parameters for the TAP waveforms shown in Figure 4.

Table 9: Test Access Port Timing Parameters

Symbol

TCKMIN

Description

TCK minimum clock period when VCCJ = 2.5V or 3.3V

TMS setup time when VCCJ = 2.5V or 3.3V

TMS hold time when VCCJ = 2.5V or 3.3V

TDI setup time when VCCJ = 2.5V or 3.3V

TDI hold time when VCCJ = 2.5V or 3.3V

TDO valid delay when VCCJ = 2.5V or 3.3V

Min

67

8

Max

–

Units

ns

TMSS

TMSH

TDIS

–

ns

25

8

–

ns

–

ns

TDIH

25

–

–

ns

TDOV

22

ns

DS123 (v2.18) May 19, 2010

www.xilinx.com

Product Specification

7

XILINX [ XILINX, INC ]

XILINX [ XILINX, INC ]