X24F064/032/016

Flow 1. ACK Polling Sequence

After the receipt of each byte, the five low order ad-

dress bits are internally incremented by one. The high

order bits of the sector address remain constant. If the

master should transmit more or less than 32 bytes prior

to generating the stop condition, the contents of the

sector cannot be guaranteed. All inputs are disabled

until completion of the internal program cycle. Refer to

Figure 5 for the address, acknowledge and data trans-

fer sequence.

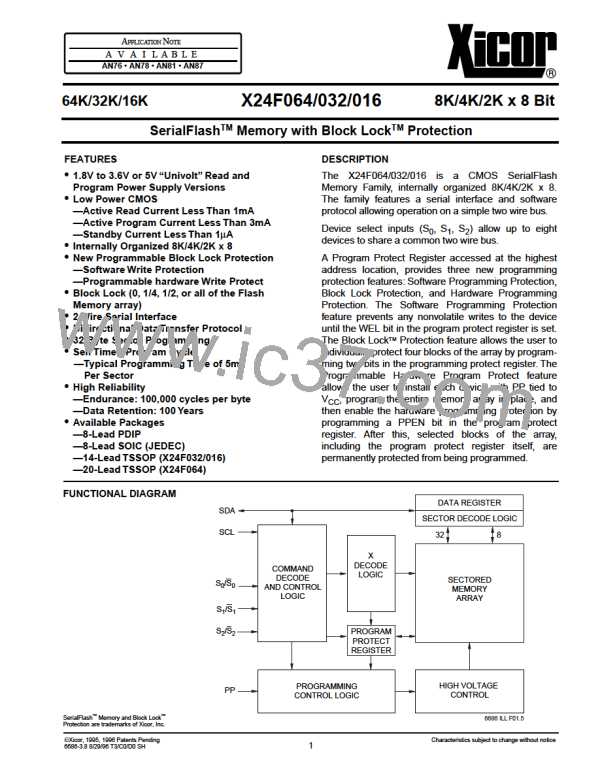

PROGRAM OPERATION

COMPLETED

ENTER ACK POLLING

ISSUE

START

Acknowledge Polling

The Max Write Cycle Time can be significantly reduced

using Acknowledge Polling. To initiate Acknowledge

Polling, the master issues a start condition followed by

the Slave Address Byte for a write or read operation. If

the device is still busy with the high voltage cycle, then

no ACK will be returned. If the device has completed

the write operation, an ACK will be returned and the

host can then proceed with the read or write operation.

Refer to Flow 1.

ISSUE SLAVE

ADDRESS AND R/W = 0

ISSUE STOP

ACK

NO

RETURNED?

YES

READ OPERATIONS

NEXT

NO

Read operations are initiated in the same manner as

program operations with the exception that the R/W bit

of the slave address is set HIGH. There are three basic

read operations: current address read, random read

and sequential read.

OPERATION

A WRITE?

YES

ISSUE SECTOR

ADDRESS

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read op-

eration, the master must either issue a stop condition

during the ninth cycle or hold SDA HIGH during the

ninth clock cycle and then issue a stop condition.

ISSUE STOP

PROCEED

PROCEED

6686 ILL F09.1

6

XICOR [ XICOR INC. ]

XICOR [ XICOR INC. ]