W9412G6JH

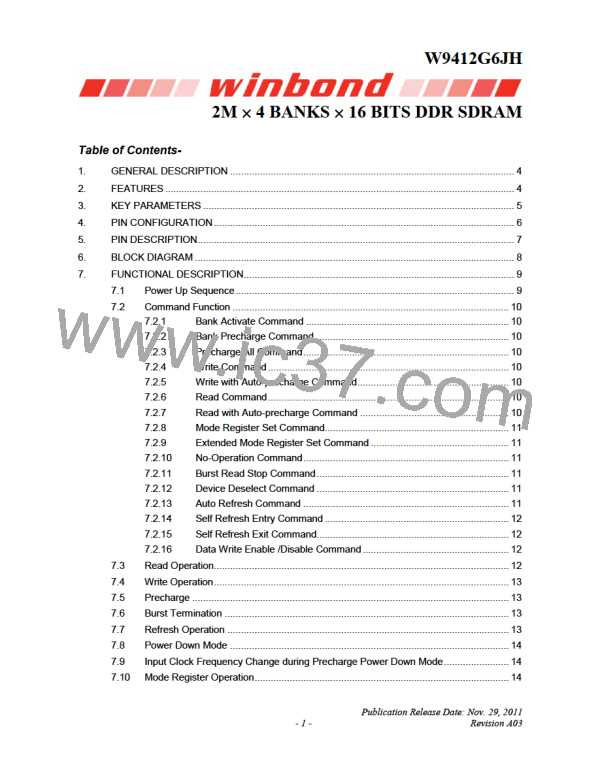

Function Truth Table, continued

CURRENT

ADDRESS

COMMAND

ACTION

NOTES

CS RAS CAS

STATE

WE

H

L

L

L

L

L

L

L

L

X

H

H

H

H

L

X

H

H

L

X

H

L

X

DSL

NOP

BST

NOP->Row active after tWR

NOP->Row active after tWR

ILLEGAL

X

X

H

L

BA, CA, A10

BA, CA, A10

BA, RA

BA, A10

X

READ/READA

WRIT/WRITA

ACT

ILLEGAL

3

3

3

3

Write

L

ILLEGAL

Recovering

H

H

L

H

L

ILLEGAL

L

PRE/PREA

AREF/SELF

MRS/EMRS

ILLEGAL

L

H

L

ILLEGAL

L

L

Op-Code

ILLEGAL

NOP->Enter precharge after

tWR

H

L

X

H

X

H

X

H

X

X

DSL

NOP->Enter precharge after

tWR

NOP

L

L

L

L

L

L

L

H

L

L

L

L

L

H

H

H

H

L

H

L

L

H

L

X

BST

ILLEGAL

Write

Recovering

with Auto-

precharge

BA, CA, A10

READ/READA

WRIT/WRITA

ACT

ILLEGAL

3

3

3

3

L

BA, CA, A10

ILLEGAL

H

H

L

H

L

BA, RA

ILLEGAL

L

BA, A10

PRE/PREA

AREF/SELF

MRS/EMRS

DSL

ILLEGAL

L

H

L

X

ILLEGAL

L

L

Op-Code

ILLEGAL

X

H

H

H

L

X

H

H

L

X

H

L

X

X

X

X

X

X

X

NOP->Idle after tRC

NOP->Idle after tRC

ILLEGAL

NOP

BST

Refreshing

H

X

X

X

READ/WRIT

ACT/PRE/PREA

ILLEGAL

H

L

ILLEGAL

L

AREF/SELF/MRS/EMRS ILLEGAL

X

X

DSL

NOP->Row after tMRD

L

L

L

H

H

H

H

H

L

H

L

X

X

X

NOP

NOP->Row after tMRD

ILLEGAL

Mode

Register

Accessing

BST

X

READ/WRIT

ILLEGAL

ACT/PRE/PREA/ARE

F/SELF/MRS/EMRS

L

L

X

X

X

ILLEGAL

Notes

1. All entries assume that CKE was active (High level) during the preceding clock cycle and the current clock cycle.

2. Illegal if any bank is not idle.

3. Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the

state of that bank.

4. Illegal if tRCD is not satisfied.

5. Illegal if tRAS is not satisfied.

6. Must satisfy burst interrupt condition.

7. Must avoid bus contention, bus turn around, and/or satisfy write recovery requirements.

8. Must mask preceding data which don’t satisfy tWR

Remark: H = High level, L = Low level, X = High or Low level (Don’t Care), V = Valid data

Publication Release Date: Nov. 29, 2011

- 20 -

Revision A03

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]