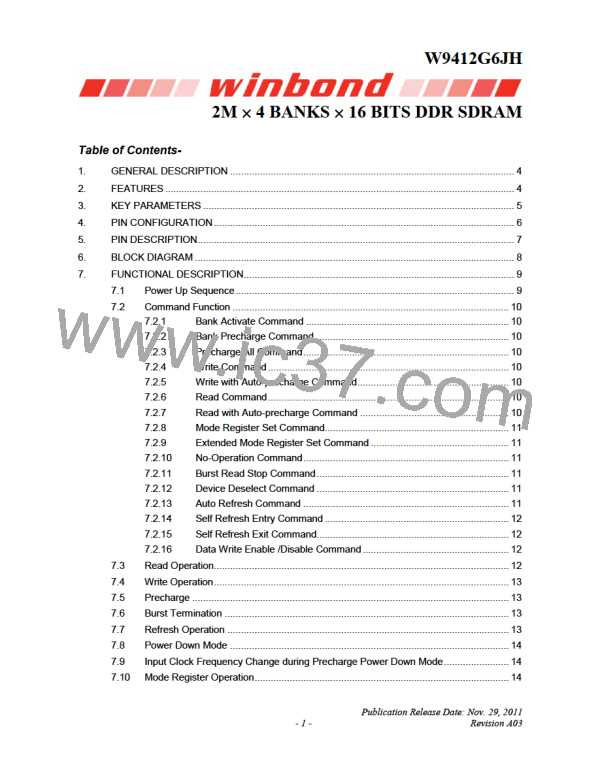

W9412G6JH

7.10.1

7.10.2

7.10.3

7.10.4

7.10.5

7.10.6

7.10.7

Burst Length field (A2 to A0)...................................................................... 14

Addressing Mode Select (A3) .................................................................... 15

CAS Latency field (A6 to A4) ..................................................................... 16

DLL Reset bit (A8) ..................................................................................... 16

Mode Register/Extended Mode register change bits (BA0, BA1).............. 16

Extended Mode Register field.................................................................... 16

Reserved field ............................................................................................ 16

8.

9.

OPERATION MODE ................................................................................................................. 17

8.1

8.2

8.3

8.4

Simplified Truth Table................................................................................................... 17

Function Truth Table..................................................................................................... 18

Function Truth Table for CKE....................................................................................... 21

Simplified Stated Diagram ............................................................................................ 22

ELECTRICAL CHARACTERISTICS......................................................................................... 23

9.1

9.2

9.3

9.4

9.5

9.6

9.7

Absolute Maximum Ratings.......................................................................................... 23

Recommended DC Operating Conditions .................................................................... 23

Capacitance.................................................................................................................. 24

Leakage and Output Buffer Characteristics.................................................................. 24

DC Characteristics........................................................................................................ 25

AC Characteristics and Operating Condition................................................................ 26

AC Test Conditions....................................................................................................... 27

10.

SYSTEM CHARACTERISTICS FOR DDR SDRAM................................................................. 30

10.1 Table 1: Input Slew Rate for DQ, DQS, and DM .......................................................... 30

10.2 Table 2: Input Setup & Hold Time Derating for Slew Rate ........................................... 30

10.3 Table 3: Input/Output Setup & Hold Time Derating for Slew Rate ............................... 30

10.4 Table 4: Input/Output Setup & Hold Derating for Rise/Fall Delta Slew Rate................ 30

10.5 Table 5: Output Slew Rate Characteristics (X16 Devices only) ................................... 30

10.6 Table 6: Output Slew Rate Matching Ratio Characteristics ......................................... 31

10.7 Table 7: AC Overshoot/Undershoot Specification for Address and Control Pins......... 31

10.8 Table 8: Overshoot/Undershoot Specification for Data, Strobe, and Mask Pins.......... 32

10.9 System Notes:............................................................................................................... 33

TIMING WAVEFORMS............................................................................................................. 35

11.1 Command Input Timing ................................................................................................ 35

11.2 Timing of the CLK Signals ............................................................................................ 35

11.3 Read Timing (Burst Length = 4) ................................................................................... 36

11.4 Write Timing (Burst Length = 4).................................................................................... 37

11.5 DM, DATA MASK (W9412G6JH) ................................................................................. 38

11.6 Mode Register Set (MRS) Timing................................................................................. 39

11.

Publication Release Date: Nov. 29, 2011

- 2 -

Revision A03

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]