W83759A

Continued

when ADV_P

= 1

IDEN1

IDEN0

Primary IDE

Secondary IDE

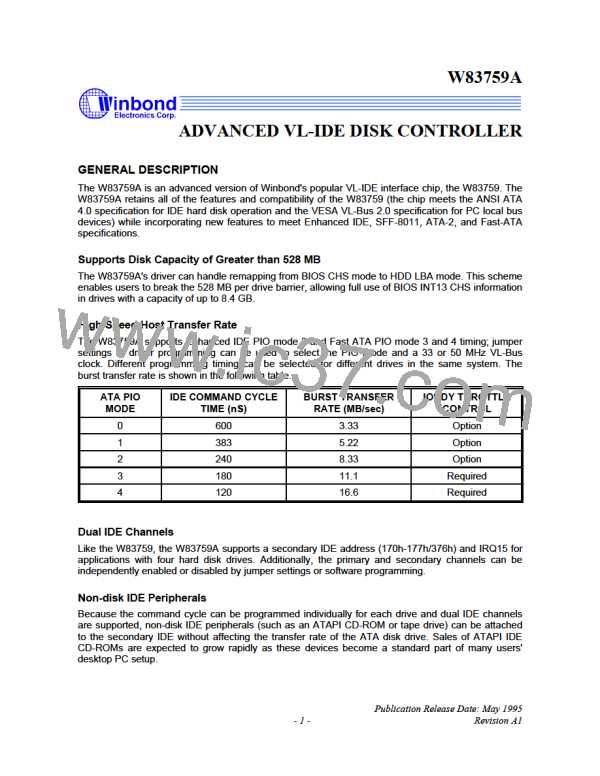

0

1

0

1

0

0

1

1

disabled

disabled

enabled

enabled

disabled

enabled

disabled

enabled

CRX81h (POSP1)

Read / Write

Power-on Setting Programming 1

Bit 7

Bit 6

Bit 5

Bit 4

MD0_P

Bit 3

PRDYEN_P

Bit 2

Bit 1

Bit 0

ADV_P

SP1_P

MD1_P

SRDYEN_P

IDEN1_P IDEN0_P

After power-on, the content of the POSP1 register is equal to that of the POSS1 register. The host

can program POSP1 to modify the power-on settings.

Bit 7

Bit 6

ADV_P

SP1_P

Programming application mode

0

1

No advanced mode application

Advanced mode application

Select VESA bus operating CLK

0

1

VLCLK 33 MHz

VLCLK > 33 MHz

Bit 5, 4

MD1_P,

MD0_P

Select default HDD host transfer mode

MD1_P MD0_P

0

0

1

1

0

1

0

1

Mode 0 (cycle time = 600 nS)

Mode 0+ (cycle time = 500 nS)

Mode 1 (cycle time = 400 nS)

Mode 2 (cycle time = 240 nS)

Bit 3

Bit 2

PRDYEN_P

SRDYEN_P

Primary channel IOCHRDY flow control

0

1

Disable IOCHRDY flow control

Enable IOCHRDY flow control

Secondary channel IOCHRDY flow control

0

1

Disable IOCHRDY flow control

Enable IOCHRDY flow control

Bit 1, 0

IDEN1_P,

IDEN0_P

IDE ENable control

Publication Release Date: May 1995

Revision A1

- 13 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]