VSC7961

Data Sheet

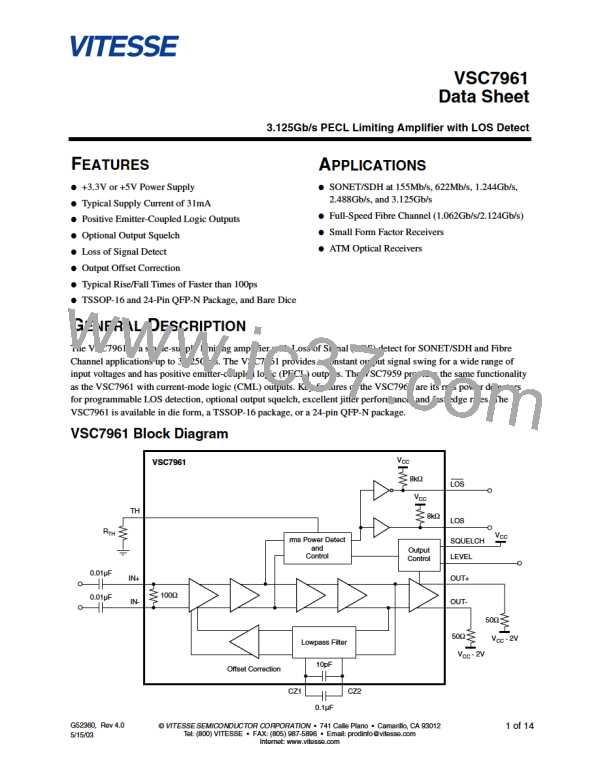

CZ1

CZ2

GND

IN+

1

2

3

4

5

6

7

8

NC

16

15

14

13

12

11

10

9

SQUELCH

VCC

OUT+

OUT−

VCC

VSC7961

Top View

IN-

GND

NC

LOS

TH

LOS

Figure 3. Pin Diagram for TSSOP-16 (YD)

Table 8. Pin Identification for TSSOP-16 (YD)

Pin Name

Pin Number

Description

CZ1

1

Offset Correction Loop Capacitor. Place capacitor between this pin and CZ2 to alter time con-

stant of offset correction loop. See “Functional Description” on page 4.

CZ2

2

Offset Correction Loop Capacitor. Place capacitor between this pin and CZ1 to alter time con-

stant of offset correction loop. See “Functional Description” on page 4.

GND

IN+

3

4

5

6

7

Supply ground.

Noninverted input signal.

Inverted input signal.

Supply ground.

IN–

GND

NC

This pin may be either connected to ground or left unconnected. This pin does not affect the per-

formance of the device.

TH

8

9

Loss of Signal (LOS) Threshold. Connect a resistor from this pin to ground to set the input signal

level at which LOS outputs will be asserted.

LOS

LOS

Inverted Loss of Signal Output. LOS is HIGH for input signals above the threshold programmed

by TH. See “Functional Description” on page 4.

10

Noninverted Loss of Signal Output. LOS is LOW for input signals above the threshold pro-

grammed by TH. See “Functional Description” on page 4.

VCC

11

12

13

14

15

Power supply.

OUT–

OUT+

VCC

Inverted data output.

Noninverted data output.

Power supply.

SQUELCH

Squelch Input. Squelch is disabled if this pin is unconnected or set LOW. When SQUELCH is

HIGH, OUT+ and OUT– are forced to static levels. See “Functional Description” on page 4.

NC

16

No connection.

10 of 14

G52360, Rev 4.0

5/15/03

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]