VITESSE

SEMICONDUCTOR CORPORATION

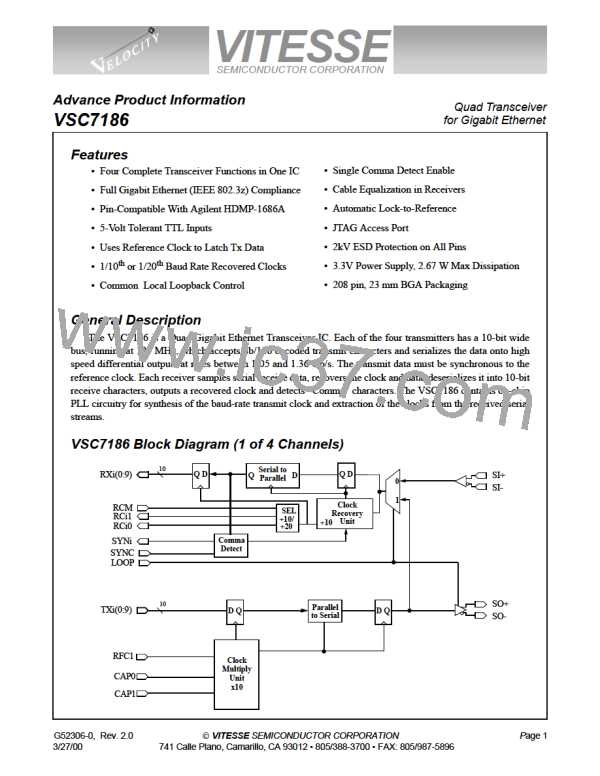

Advance Product Information

Quad Transceiver

for Gigabit Ethernet

VSC7186

Table 1: Transmission Order and Mapping of a 10b Character

T9

j

T8

h

T7

g

T6

f

T5

i

T4

e

T3

d

T2

c

T1

b

T0

a

Data Bit

10B Bit Position

Comma Character

x

x

x

1

1

1

1

1

0

0

Clock Recovery

The VSC7186 accepts differential high speed serial input from the selected source (either the PECL SIi+/-

pins or the internal SOi+/- data), extracts the clock and retimes the data. Equalizers are included in the receiver

to open the data eye and compensate for Intersymbol Interference (ISI) which may be present in the incoming

data. The serial bit stream should be encoded so as to provide DC balance and limited run length by an 8b/10b

encoding scheme. The digital Clock Recovery Unit (CRU) is completely monolithic and requires no external

components. For proper operation, the baud rate of the data stream to be recovered should be within +200 ppm

of ten times the REF frequency. For example, Gigabit Ethernet systems use 125 MHz oscillators with a +/-

100ppm accuracy resulting in +/-200 ppm between VSC7186 pairs.

Deserializer

The recovered serial bit stream is converted into a 10-bit parallel output character. The VSC7186 provides

complementary TTL recovered clocks, RCi0 and RCi1, at one-twentieth of the serial baud rate if RCM=LOW,

or a single clock at one-tenth the serial baud rate, on RCi1 only, if RCM=HIGH. The clocks are generated by

dividing down the high-speed recovered clock which is phase locked to the serial data. The serial data is

retimed, deserialized and output on Ri(0:9).

If serial input data is not present, or does not meet the required baud rate, the VSC7186 will continue to

produce a recovered clock so that downstream logic may continue to function. The RCi0/RCi1 output frequency

under these circumstances will differ from its expected frequency by no more than +1%.

Word Alignment

The VSC7186 provides 7-bit comma character recognition and data word alignment. Word synchronization

is enabled on all channels by asserting SYNC HIGH. When synchronization is enabled, the receiver examines

the recovered serial data for the presence of the “Comma” pattern. This pattern is “0011111XXX”, where the

leading zero corresponds to the first bit received. The comma sequence is not contained in any normal 8b/10b

coded data character or pair of adjacent characters. It occurs only within special characters, known as K28.1,

K28.5 and K28.7, which are defined for synchronization purposes. Improper comma alignment is defined as

any of the following conditions:

1) The comma is not aligned within the 10-bit transmission character such that Ri(0..6) = “0011111”.

2) The comma straddles the boundary between two 10-bit transmission characters.

3) The comma is properly aligned but occurs in the received character presented during the rising edge of

RCi0 rather than RCi1.

When an improperly aligned comma is encountered, the recovered clock is stretched, never slivered, so that

the comma character and recovered clocks are aligned properly to Ri(0:9). This results in proper character and

word alignment. When the parallel data alignment changes in response to a improperly aligned comma pattern,

G52306-0, Rev. 2.0

3/27/00

VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 3

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]