UCC28180

SLUSBQ5A –NOVEMBER 2013–REVISED NOVEMBER 2013

www.ti.com

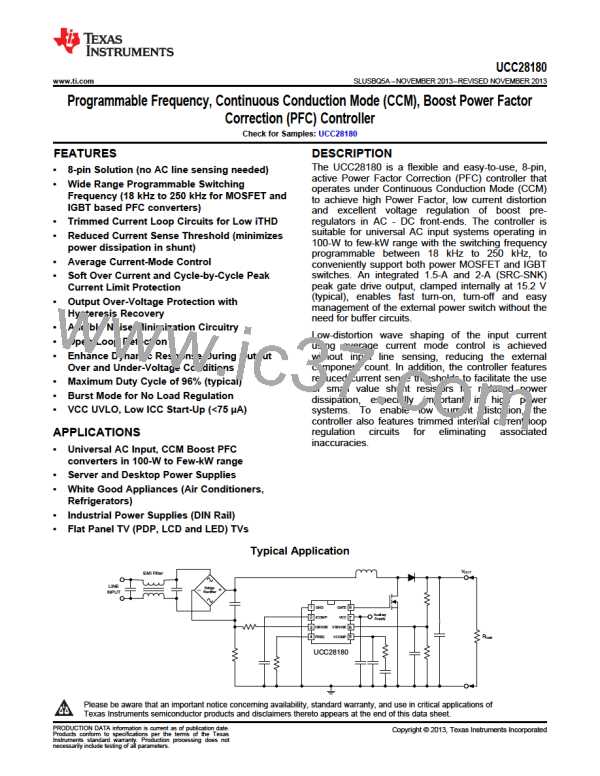

Output Over-Voltage Detection (OVD), Under-Voltage Detection (UVD) and Enhanced Dynamic

Response (EDR)

During normal operation, small perturbations on the PFC output voltage rarely exceed ±5% deviation and the

normal voltage control loop gain drives the output back into regulation. For large changes in line or load, if the

output voltage perturbation exceeds ±5%, an output over-voltage (OVD) or under-voltage (UVD) is detected and

Enhanced Dynamic Response (EDR) acts to speed up the slow response of the low-bandwidth voltage loop.

During EDR, the transconductance of the voltage error amplifier is increased approximately five times to speed

charging or discharging the voltage-loop compensation capacitors to the level required for regulation. EDR is

disabled when 5.25 V > VSENSE > 4.75 V. The EDR feature is not activated until soft start is completed. The

UVD is disabled during soft over protection (SOC) condition (since UVD and SOC conflict with each other).

Over Voltage Protection

Enhanced Dynamic Response

Open Loop Protection/ Standby

Soft-Start Complete

+

OVP_L

5.35V

+

OVP_H

5.45V

S

R

Q

Q

OVERVOLTAGE

PROTECTION

+

5.10V

Output Voltage

Standby

EDR

EDR

+

+

RFB1

VSENSE

OVERVOLTAGE

DETECTION

5.25V

UNDERVOLTAGE

DETECTION

4.75V

4.9V

RFB2

Optional

END OF SS

SOFT-START COMPLETE

+

+

OPEN LOOP

PROTECTION/STANDBY

OLP/STANDBY

0.82V

Figure 26. OVP_H, OVP_L, EDR, OLP, Soft Start Complete

16

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links :UCC28180

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]