UCC28070-Q1

www.ti.com

SLUSA71A –JULY 2010–REVISED JUNE 2011

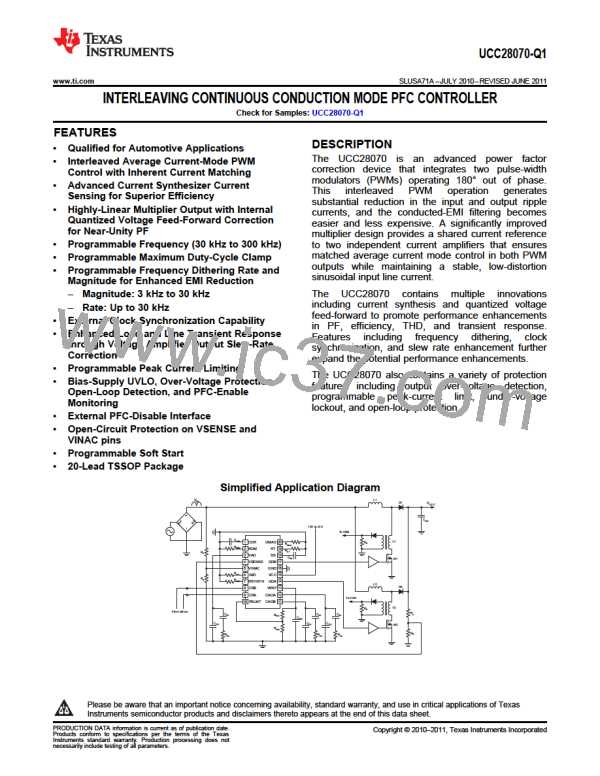

Functional Block Diagram

VSENSE

+

OVP

3.18V

3.08V

VCC 15

VREF 13

GND 16

Fault

0.75V

25V

+

ReStart

Ext.Disable

oC

0.60V

160On

140 Off

ThermSD

SS

+

Linear

EN

6V

Regulator

8V

S

R

Q

Q

0.75V

0.60V

+

VSENSE

0.90V

0.75V

+

UVLO

ZeroPwr

10.2V

9.2V

VAO

+

6

5

IMO

VINAC

20

19

Voltage

Feed-

DMAX

RT

250nA

CLKA

CLKB

OffA

Forward

VVINAC * (VVAO –1)

Oscillator w/

Freq. Dither

I

=

* 17uA

x

IMO

KVFF

KVFF

OffB

Mult.

/

x

3

VAO

SS

4V

+

ReStart

RDM/

SYNC

Logic

2

1

100uA

SYNC

5V

Slew Rate

Correction

2.8V

SYNC Dither

Enable Disable

+

10uA

+

CDR

5V

GmAmp

-

4

VSENSE

+

VA

3V

+

250nA

Adaptive SS

1mA

10

9

PKLMT

CSA

IpeakA

ReStart

ISS

10uA

+

+

Control

Logic

ReStart

Ext.Disable

IpeakB

+

18 SS

PWM1

+

CA1

VCC

GmAmp

+

S

R

Q

Q

(Clamped at 13.5V)

Driver 14 GDA

GND

OutA

OffA

IpeakA

CLKA

CSB

8

7

OutB

Current

Fault

PWM2

Synthesizer

Disable

RSYNTH

+

CA2

VCC

(Clamped at 13.5V)

+

VINAC

S

R

Q

Q

GmAmp

+

5V

VSENSE

OffB

IpeakB

CLKB

Driver

17

GDB

CAOA 12

CAOB 11

Fault

GND

Copyright © 2010–2011, Texas Instruments Incorporated

9

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]