UCC21759-Q1

SLUSEB4A – AUGUST 2020 – REVISED DECEMBER 2020

www.ti.com

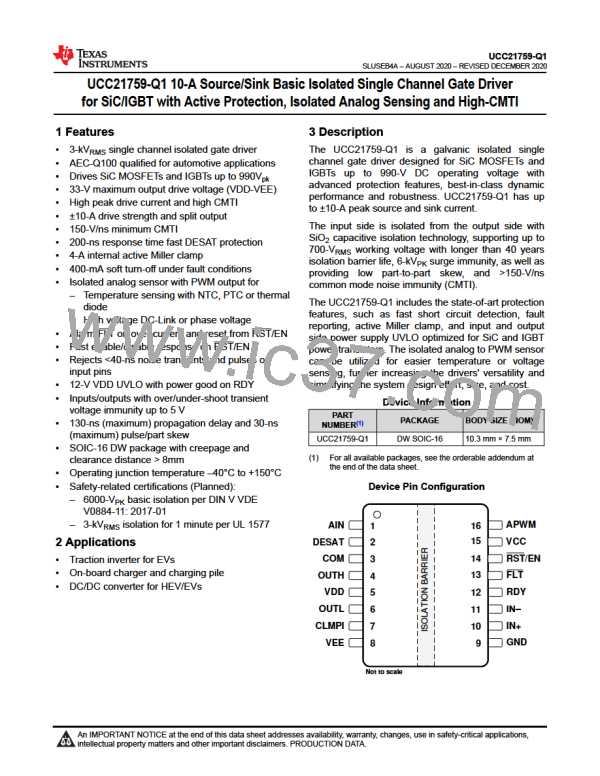

7.4.2 VDD UVLO

The VDD UVLO protection details are discussed in this section. Figure 7-9 shows the timing diagram illustrating

the definition of UVLO ON/OFF threshold, deglitch filter, response time, RDY and AIN–APWM.

IN

(”IN+‘ Å ”INÅ‘)

tVDDFIL

VDD

tVDDÅ to OUT

VVDD_ON

VVDD_OFF

COM

VEE

VCC

tVDD+ to OUT

VCLMPTH

OUT

90%

tRDYHLD

10%

tVDD+ to RDY

tVDDÅ to RDY

RDY

Hi-Z

VCC

APWM

Figure 7-9. VDD UVLO Protection Timing Diagram

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

23

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]