ꢀ ꢁꢂ ꢃꢄ ꢂꢅ

ꢀ ꢁꢂ ꢃꢄ ꢂꢆ

SLUS557B − MARCH 2003 − REVISED APRIL 2004

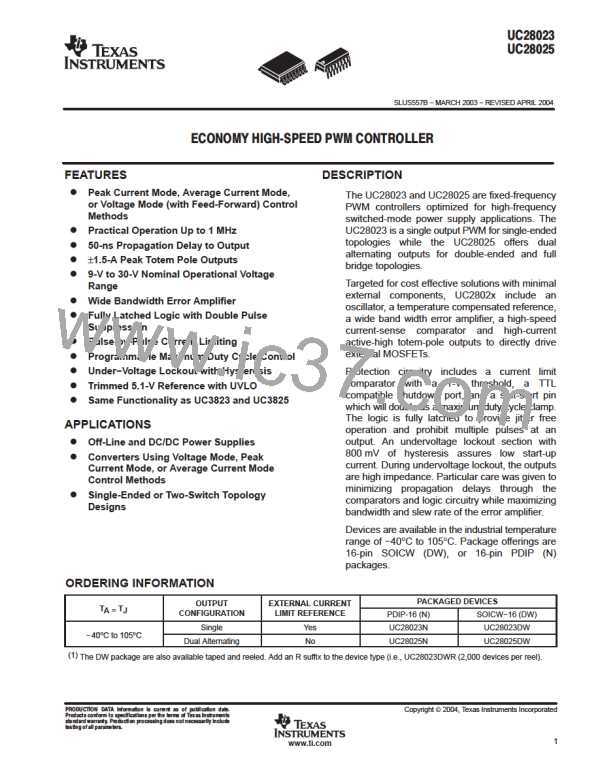

ELECTRICAL CHARACTERISTICS

T

= −40°C to 105°C , T = T

A,

R

= 3.65 kΩ, C = 1 nF, V

CC

= 15 V (unless otherwise noted)

A

J

T

T

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

REFERENCE

V

REF

Reference voltage

T = 25°C,

I = 1 mA

REF

5.05

5.10

2

5.15

15

V

J

Line regulation voltage

Load regulation voltage

10 V ≤ V

≤ 30 V

CC

mV

1 mA ≤ I

≤ 10 mA

5

15

REF

(1)

Temperature stability

T

(min)

< T < T

(max)

0.2

0.4 mV/°C

A

(1)

Total output voltage variation

Line, load, temperature

10 Hz < f < 10 kHz

4.95

5.25

V

(1)

Output noise voltage

50

5

µV

mV

mA

(1)

Long term stability voltage

T = 125°C,

J

1000 hours

25

I

Short circuit current

V

REF

= 0 V

−20

360

−50

−100

SS

OSCILLATOR

Initial accuracy

(1)

(1)

f

T = 25°C

J

400

0.2%

5%

440

kHz

kHz

V

OSC

Voltage stability

Temperature stability

10 V ≤ V

CC

≤ 30 V

2.0%

(1)

(1)

T

(min)

< T < T

(max)

A

Total voltage variation

Line, temperature

340

3.9

460

V

High-level clock output voltage

Low-level clock output voltage

4.5

2.3

CLOCK_H

V

2.9

3.0

CLOCK_L

(1)

Ramp peak voltage

V

2.6

0.70

1.6

2.8

RAMP(p)

RAMP(v)

(1)

Ramp valley voltage

V

1.00

1.8

1.25

2.0

(1)

V

Ramp vally-to-peak voltage

RAMP(v-p)

ERROR AMPLIFIER

V

Input offset voltage

Input bias current

Input offset current

Open loop gain

15

3.0

1.0

mV

IN

I

0.6

0.1

95

BIAS

IN

µA

I

A

VOL

1 V ≤ V

OUT

≤ 4 V

60

75

CMRR

PSRR

Common mode rejection ratio

Power supply rejection ratio

Output sink current

1.5 V ≤ V

CM

≤ 5.5 V

95

dB

10 V ≤ V

CC

≤ 30 V

85

110

2.5

−1.3

4.7

0.5

5.5

12

I

V

= 1 V

= 4 V

1.0

−0.5

4.0

0

OUT(sink)

(EAOUT)

(EAOUT)

(EAOUT)

(EAOUT)

mA

V

Output source current

V

IOUT(src)

V

V

High-level output voltage

Low-level output voltage

I

I

= −0.5 mA

= 1 mA

5.0

1.0

OH

OL

(1)

Unity gain bandwidth

3.0

6

MHz

(1)

Slew rate

V/µs

PWM COMPARATOR

I

RAMP bias current

V

= 0 V

−1

90%

45%

−5

µA

BIAS

RAMP

UC28023

UC28025

UC28023

UC28025

80%

40%

Maximum duty cycle

(2)

0%

0%

Minimum duty cycle

EAOUT zero DC threshold

(1)

V

= 0 V

1.10

1.25

50

1.40

100

V

RAMP

t

Delay to output time

ns

DELAY

(1)

(2)

Ensured by design. Not production tested.

Tested as 80% minimum for the oscillator which is the equivalent of 40% for UC28025.

3

www.ti.com

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]