TPS65163

www.ti.com

SLVSA28 –OCTOBER 2009

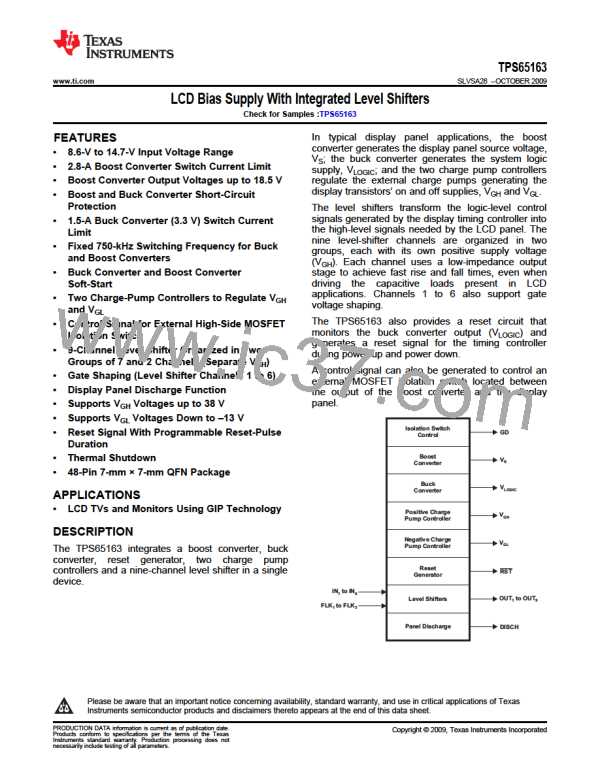

DETAILED DESCRIPTION

GD

SW

SW

SS

VL

VIN

LDO

VL

PGND

PGND

Boost

Converter

Bandgap

VREF

OVP & SCP

Comparator

VREF

+

-

-

Switching

Enable

VIN

+

-

GD

Enable

FB

CTRLP

FBP

+

VREF

+

-

COMP

VREF

Enable

750 kHz

Clock

VIN

VIN

DLY

Timer

EN

CRST

EN

Timer

RST

Buck

Converter

Q

Bootstrap

Capacitor

SWB

FBB

S

Latch

R

PG

Enable

VREF

+

-

FBN

+

-

UVLO

VL

Z

CTRLN

AGND

-

VIN

UVLO

+

VREF

VGH1

FLK1

FLK2

FLK3

IN1

RE

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

Gate

Shaping

IN2

IN3

IN4

Level

Shifters

IN5

IN6

IN7

VSENSE

-

DISCHARGE

VGL

VREF

+

VGH2

IN8

OUT8

OUT9

Level

Shifter

IN9

Figure 37. TPS65163 Internal Block Diagram

Copyright © 2009, Texas Instruments Incorporated

Submit Documentation Feedback

15

Product Folder Link(s) :TPS65163

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]