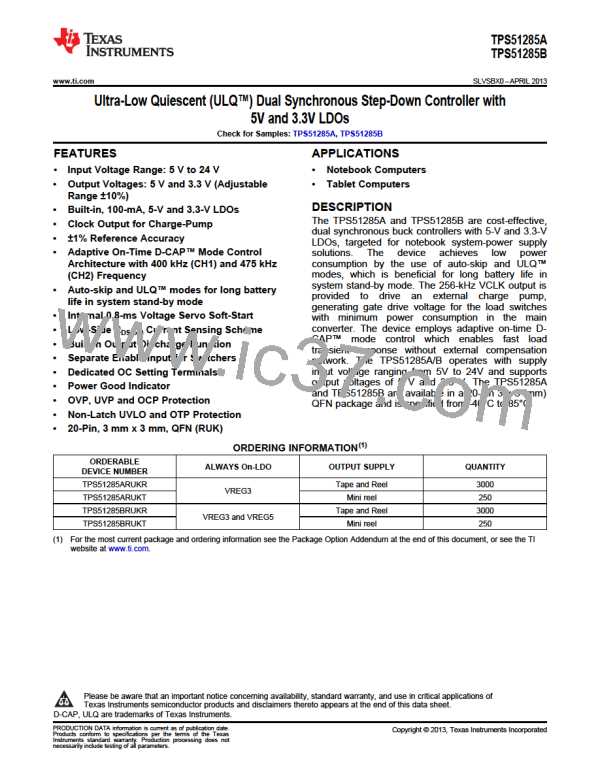

TPS51285A

TPS51285B

SLVSBX0 –APRIL 2013

www.ti.com

Layout Considerations

Good layout is essential for stable power supply operation. Follow these guidelines for an efficient PCB layout.

Placement

•

•

Place voltage setting resistors close to the device pins.

Place bypass capacitors for VREG5 and VREG3 close to the device pins.

Routing (Sensitive analog portion)

•

•

Use small copper space for VFBx. There are short and narrow traces to avoid noise coupling.

Connect VFB resistor trace to the positive node of the output capacitor. Routing inner layer away from power

traces is recommended.

•

Use short and wide trace from VFB resistor to vias to GND (internal GND plane).

Routing (Power portion)

•

•

Use wider/shorter traces of DRVL for low-side gate drivers to reduce stray inductance.

Use the parallel traces of SW and DRVH for high-side MOSFET gate drive in a same layer or on adjoin

layers, and keep them away from DRVL.

•

•

Use wider/ shorter traces between the source terminal of the high-side MOSFET and the drain terminal of the

low-side MOSFET

Thermal pad is the GND terminal of this device. Five or more vias with 0.33-mm (13-mils) diameter connected

from the thermal pad to the internal GND plane should be used to have strong GND connection and help heat

dissipation.

20

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: TPS51285A TPS51285B

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]