TMDS361

SLLS919–DECEMBER 2008............................................................................................................................................................................................ www.ti.com

SINK

HPD

5V

VCC

(3.3 V)

VDD

(5 V)

HPD

5V

HPD1

SDA SCL

mController

CEC

EQ

5V

47kW

SDA1

SCL1

S1

S2

SDA

SCL

CEC

SOURCE 1

With AC Coupled

HDMI Output

SDA

SCL

CEC

LOGIC

CEC

E-EDID

A11/B11

A12/B12

A13/B13

A14/B14

CLK

D0

CLK

D0

D1

D2

D1

D2

CEC

PHY

HPD2

HPD_SINK

HPD

5V

HPD

5V

1kW

1kW

5V

47kW

3.3V

4.7kW

SDA2

SCL2

SDA

SCL

CEC

SDA

SCL

CEC

4.7kW

SDA_SINK

SCL_SINK

SOURCE 2

With DC Coupled

HDMI Output

DDC_SDA

DDC_SCL

CEC

E-EDID

A21/B21

A22/B22

A23/B23

A24/B24

CLK

D0

CLK

D0

HDMI RX

D1

D2

D1

D2

Y1/Z1

Y2/Z2

Y3/Z3

Y4/Z4

Y1/Z1

Y2/Z2

Y3/Z3

Y4/Z4

HPD3

HPD

5V

HPD

5V

1kW

5V

47kW

SDA3

SCL3

SDA

SCL

CEC

SDA

SCL

CEC

VSADJ

SOURCE 3

in General

HDMI Output

4.02 kW 10%

CEC E-EDID

A31/B31

A32/B32

A33/B33

A34/B34

CLK

D0

CLK

D0

D1

D2

D1

D2

GND

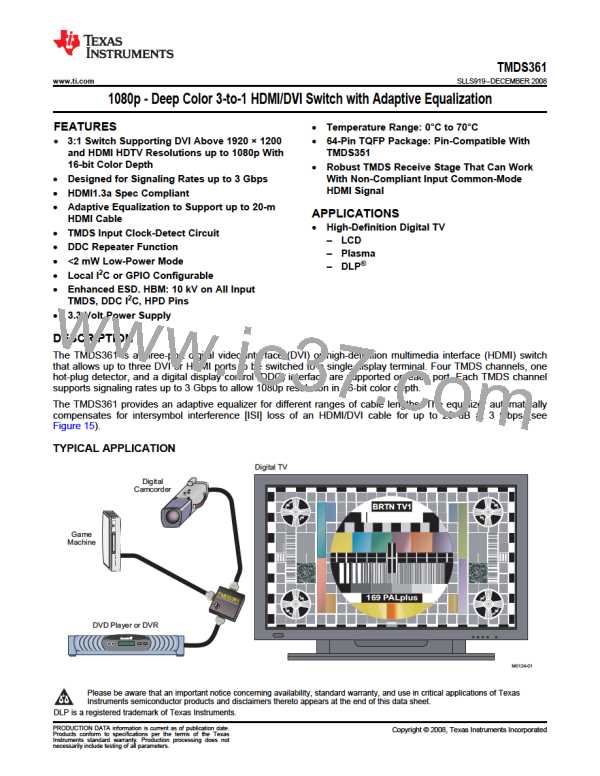

Figure 35. Three-Port HDMI-Enabled DTV With TMDS361 – CEC Commands Active

I2C INTERFACE NOTES

The I2C interface is used to access the internal registers of the TMDS361. I2C is a two-wire serial interface

developed by Philips Semiconductor (see I2C-Bus Specification, Version 2.1, January 2000). The bus consists of

a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is idle, both SDA and SCL lines

are pulled high. All the I2C-compatible devices connect to the I2C bus through open-drain I/O pins, SDA and

SCL. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is

responsible for generating the SCL signal and device addresses. The master also generates specific conditions

that indicate the START and STOP of data transfer. A slave device receives and/or transmits data on the bus

under control of the master device. The TMDS361 works as a slave and supports standard-mode transfer (100

kbps).

The basic I2C start and stop access cycles are shown in Figure 36.

The basic access cycle consists of the following:

•

•

•

•

A start condition

A slave address cycle

Any number of data cycles

A stop condition

30

Submit Documentation Feedback

Copyright © 2008, Texas Instruments Incorporated

Product Folder Link(s) :TMDS361

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]