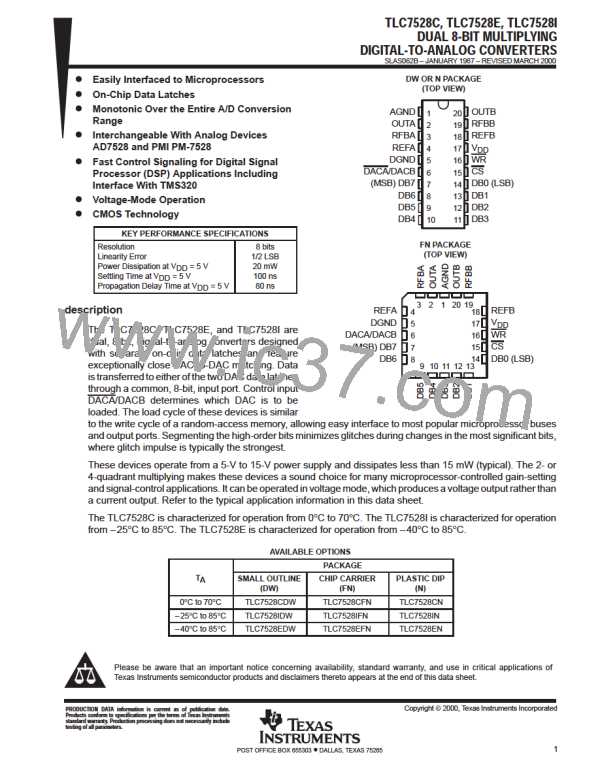

TLC7528C, TLC7528E, TLC7528I

DUAL 8-BIT MULTIPLYING

DIGITAL-TO-ANALOG CONVERTERS

SLAS062B – JANUARY 1987 – REVISED MARCH 2000

APPLICATION INFORMATION

V

R6

20 kΩ

I(A)

±10 V

(see Note B)

R1

R2 (see Note A)

(see Note A)

RFBA

OUTA

C1

R5

20 kΩ

17

14

(see Note C)

V

DD

R7

10 kΩ

DB0

–

Input

Buffer

8

8

DACA

Latch

A1

+

–

A2

+

AGND

(see Note B)

DB7

V

OA

7

6

R11

5 kΩ

R4 (see Note A)

C2

RFBB

DACA/

DACB

R8

20 kΩ

Control

Logic

15

CS

(see Note C)

16

5

–

OUTB

AGND

WR

8

8

–

DACB

REFB

Latch

A3

+

A4

+

V

OB

R9

10 kΩ

(see Note B)

DGND

AGND

R11

5 kΩ

R3

AGND

(see Note A)

R10

V

20 kΩ

(see Note B)

I(B)

±10 V

NOTES: A. R1, R2, R3, and R4 are used only if gain adjustment is required. See table in Figure 3 for recommended values. Adjust R1 for

= 0 V with code 10000000 in DACA latch. Adjust R3 for V = 0 V with 10000000 in DACB latch.

V

OA

OB

B. Matching and tracking are essential for resistor pairs R6, R7, R9, and R10.

C. C1 and C2 phase compensation capacitors (10 pF to 15 pF) may be required if A1 and A3 are high-speed amplifiers.

Figure 4. Bipolar Operation (4-Quadrant Operation)

Table 1. Unipolar Binary Code

Table 2. Bipolar (Offset Binary) Code

DAC LATCH CONTENTS

DAC LATCH CONTENTS

ANALOG OUTPUT

ANALOG OUTPUT

†

LSB

‡

LSB

MSB

MSB

1 1 1 1 1 1 1 1

–V (255/256)

1 1 1 1 1 1 1 1

V (127/128)

I

I

1 0 0 0 0 0 0 1

1 0 0 0 0 0 0 0

0 1 1 1 1 1 1 1

0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0

–V (129/256)

1 0 0 0 0 0 0 1

1 0 0 0 0 0 0 0

0 1 1 1 1 1 1 1

0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0

V (1/128)

I

I

–V (128/256) = –V /2

0 V

I

i

–V (127/256)

–V (1/128)

I

I

–V (1/256)

–V (127/128)

I

I

–V (0/256) = 0

–V (128/128)

I

I

†

–8

1 LSB = (2 )V

‡

–7

1 LSB = (2 )V

I

I

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]