SN54LVTH16373, SN74LVTH16373

3.3-V ABT 16-BIT TRANSPARENT D-TYPE LATCHES

WITH 3-STATE OUTPUTS

www.ti.com

SCBS144P–MAY 1992–REVISED NOVEMBER 2006

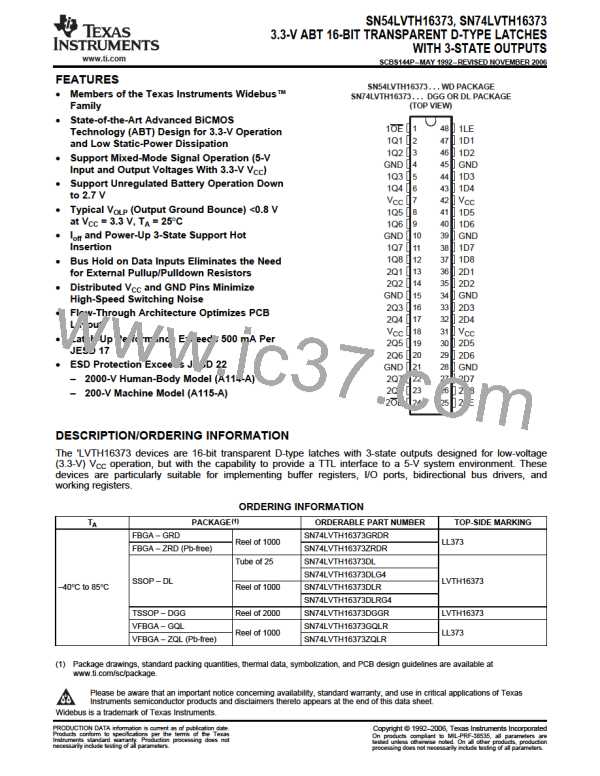

GRD OR ZRD PACKAGE

(TOP VIEW)

TERMINAL ASSIGNMENTS(1)

(54-Ball GRD/ZRD Package)

1

2

3

4

5

6

1

2

3

4

5

6

A

B

C

D

E

F

1Q1

1Q3

1Q5

1Q7

2Q1

2Q3

2Q5

2Q7

2Q8

NC

1OE

NC

1LE

NC

NC

1D1

1D3

1D5

1D7

2D1

2D3

2D5

2D7

2D8

A

B

C

D

1Q2

1Q4

1Q6

1Q8

2Q2

2Q4

2Q6

NC

1D2

1D4

1D6

1D8

2D2

2D4

2D6

NC

VCC

GND

GND

GND

VCC

NC

VCC

GND

GND

GND

VCC

NC

E

F

G

H

J

G

H

J

2OE

2LE

(1) NC – No internal connection

FUNCTION TABLE

(8-BIT SECTION)

INPUTS

OUTPUT

Q

OE

L

CLK

H

D

H

L

H

L

L

H

L

L

X

X

Q0

Z

H

X

LOGIC DIAGRAM (POSITIVE LOGIC)

1

24

2OE

1OE

25

48

2LE

1LE

C1

1D

C1

1D

2

13

2Q1

1Q1

47

36

2D1

1D1

To Seven Other Channels

Pin numbers shown are for the DGG, DL, and WD packages.

To Seven Other Channels

3

Submit Documentation Feedback

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]