DRV8874

www.ti.com

SLVSF66A –AUGUST 2019–REVISED DECEMBER 2019

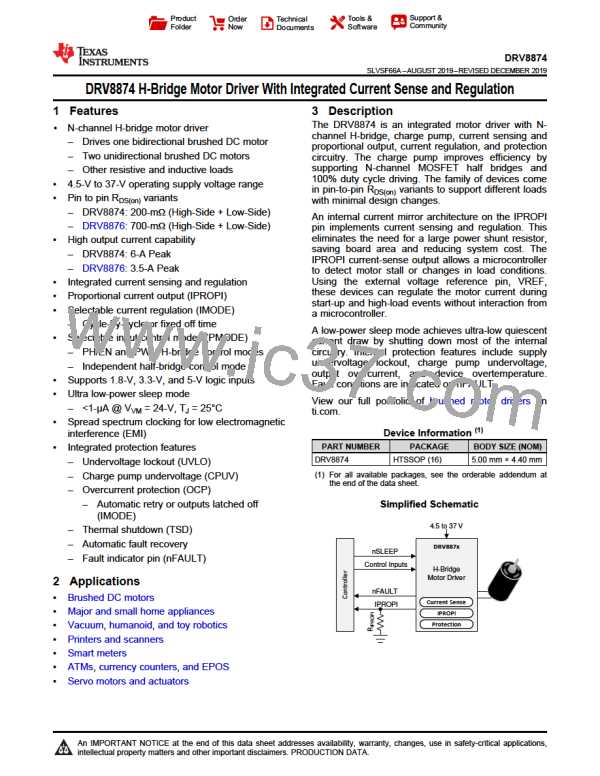

6.4 Thermal Information

DRV8874

THERMAL METRIC(1)

PWP (HTSSOP)

UNIT

16 PINS

36.0

27.3

11.1

0.4

RθJA

Junction-to-ambient thermal resistance

Junction-to-case (top) thermal resistance

°C/W

°C/W

°C/W

°C/W

°C/W

°C/W

RθJC(top)

RθJB

Junction-to-board thermal resistance

ΨJT

Junction-to-top characterization parameter

Junction-to-board characterization parameter

Junction-to-case (bottom) thermal resistance

ΨJB

11.0

2.7

RθJC(bot)

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

6.5 Electrical Characteristics

4.5 V ≤ VVM ≤ 37 V, –40°C ≤ TJ ≤ 150°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

POWER SUPPLIES (VCP, VM)

VVM = 24 V, nSLEEP = 0 V, TJ = 25°C

nSLEEP = 0 V

0.75

1

5

µA

µA

IVMQ

IVM

VM sleep mode current

VM active mode current

VVM = 24 V, nSLEEP = 5 V,

EN/IN1 = PH/IN2 = 0 V

3

7

mA

tWAKE

tSLEEP

VVCP

fVCP

Turnon time

VVM > VUVLO, nSLEEP = 5 V to active

nSLEEP = 0 V to sleep mode

1

1

ms

ms

V

Turnoff time

Charge pump regulator voltage

Charge pump switching frequency

VCP with respect to VM, VVM = 24 V

5

400

kHz

LOGIC-LEVEL INPUTS (EN/IN1, PH/IN2, nSLEEP)

VVM < 5 V

0

0

0.7

0.8

5.5

VIL

Input logic low voltage

Input logic high voltage

Input hysteresis

V

VVM ≥ 5 V

VIH

1.5

V

200

50

mV

mV

µA

µA

kΩ

VHYS

nSLEEP

VI = 0 V

VI = 5 V

To GND

IIL

Input logic low current

Input logic high current

Input pulldown resistance

–5

5

IIH

50

75

RPD

100

TRI-LEVEL INPUTS (PMODE)

VTIL

VTIZ

VTIH

ITIL

Tri-level input logic low voltage

0

0.9

0.65

1.2

V

Tri-level input Hi-Z voltage

Tri-level input logic high voltage

Tri-level input logic low current

Tri-level input Hi-Z current

Tri-level input logic high current

Tri-level pulldown resistance

Tri-level pullup resistance

1.1

V

1.5

5.5

V

VI = 0 V

–50

–10

–32

µA

µA

µA

kΩ

kΩ

ITIZ

VI = 1.1 V

VI = 5 V

10

ITIH

113

44

150

RTPD

RTPU

To GND

To internal 5 V

156

QUAD-LEVEL INPUTS (IMODE)

VQI2

RQI2

RQI3

VQI4

RQPD

RQPU

Quad-level input level 1

Quad-level input level 2

Quad-level input level 3

Quad-level input level 4

Quad-level pulldown resistance

Quad-level pullup resistance

Voltage to set quad-level 1

Resistance to GND to set quad-level 2

Resistance to GND to set quad-level 3

Voltage to set quad-level 4

To GND

0

18.6

57.6

2.5

0.45

21.4

66.4

5.5

V

20

62

kΩ

kΩ

V

136

68

kΩ

kΩ

To internal 5 V

Copyright © 2019, Texas Instruments Incorporated

Submit Documentation Feedback

5

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]