DLPA2000

www.ti.com.cn

ZHCSCO5B –JUNE 2014–REVISED FEBRUARY 2018

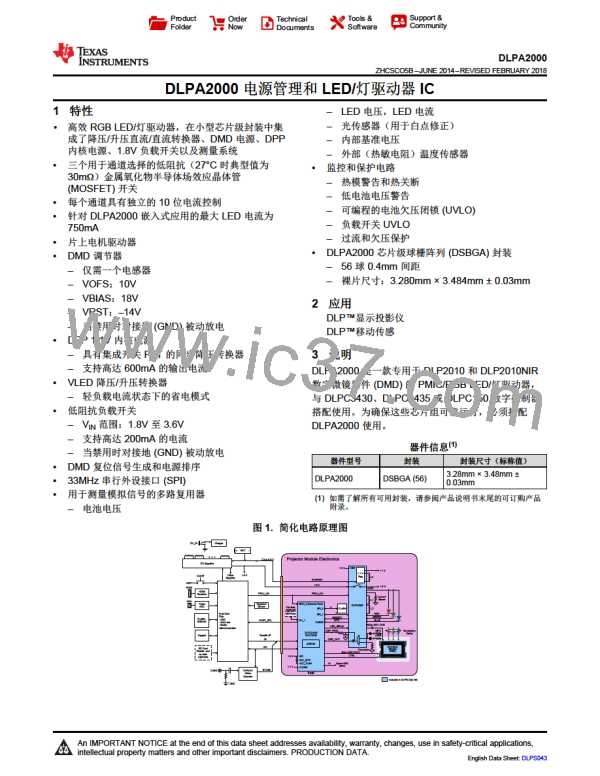

7.5 Register Maps

Table 7. Register Description

ADDRESS

REGISTER

DEFAULT

NAME

TABLE

DESCRIPTION

(HEX)

USER CONFIGURATION DEFINITIONS

R

0x00

0x01

0x02

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

0x0B

0x0C

0x0D

CHIP ID

CHIPENABLE

IREG

Figure 16

Chip revision register; DLPA2000

B3

0F

30

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

Figure 17

Enable register

Figure 18

Transient-current limit settings

Regulation current MSB, SW4

Regulation current LSB, SW4

Regulation current MSB, SW5

Regulation current LSB, SW5

Regulation current MSB, SW6

Regulation current LSB, SW6

Switch ON/OFF control (direct mode)

AFE (MUX) control

SW4MSB

SW4LSB

SW5MSB

SW5LSB

SW6MSB

SW6LSB

SWCNTRL

AFE

Figure 19

Table 12, Table 13

Figure 21

0

0

Figure 22, Table 16

Figure 23

0

0

Figure 24, Table 19

Figure 25

0

0

Figure 26

0

BBM

Figure 27, Table 22

Figure 28, Table 23

Figure 29, Table 24

Break before make timing

Interrupt register

0

INT

0

R/W

INT MASK

Interrupt mask register

DFh

Timing register VOFS, VBIAS, VRST, and

RESETZ

R/W

R/W

0x0E

0x0F

TIMING

Figure 30, Table 26

Figure 31, Table 27

7

0

MOTOR CTRL

Motor control register

USER PROTECTED DEFINITION

R/W

R/W

0x10

0x11

PASSWORD

SYSTEM

Figure 32

Figure 33

Password register

0

0

System configuration register

USER EEPROM SCRATCH PAD DEFINITION

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0x20

0x21

0x22

0x23

0x24

0x25

0x26

0x27

BYTE0

BYTE1

BYTE2

BYTE3

BYTE4

BYTE5

BYTE6

BYTE7

Figure 34

Figure 35

Figure 36

Figure 37

Figure 38

Figure 39

Figure 40

Figure 41

User EEPROM, Byte0

User EEPROM, Byte1

User EEPROM, Byte2

User EEPROM, Byte3

User EEPROM, Byte4

User EEPROM, Byte5

User EEPROM, Byte6

User EEPROM, Byte7

0

0

0

0

0

0

0

0

7.5.1 Chip Revision Register

Figure 16. Chip Revision Register, Address = 00h, HEX = B3

7

6

5

4

3

2

1

0

CHIP ID [7:0]

R

R

R

R

R

R

R

R

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset.

Table 8. Chip Revision Register Field Descriptions

BIT

7:4

3:0

FIELD

TYPE

RESET

1011

0011

DESCRIPTION

R

R

CHIPID<3:0>

REVID<3:0>

CHIP ID

Copyright © 2014–2018, Texas Instruments Incorporated

29

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]