CDC536

www.ti.com

SCAS378G–APRIL 1994–REVISED JULY 2004

FUNCTIONAL BLOCK DIAGRAM (continued)

Terminal Functions

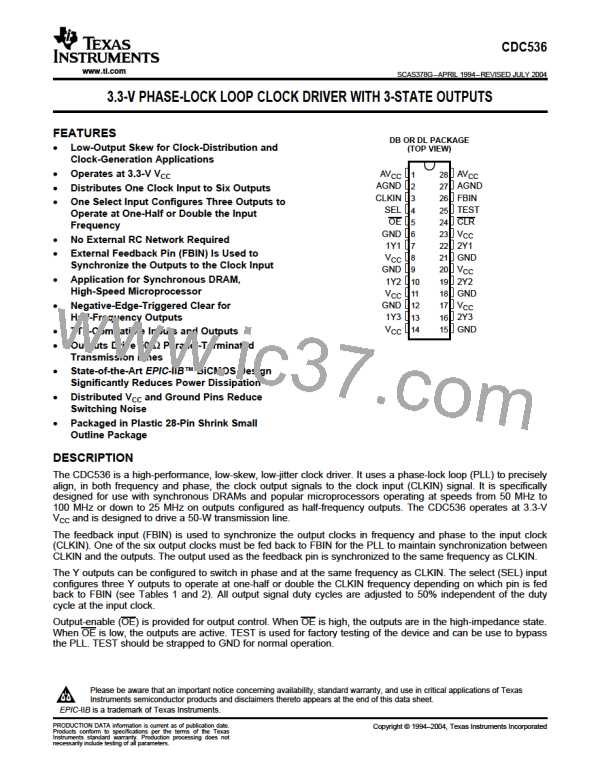

TERMINAL

I/O

DESCRIPTION

NAME

NO.

Clock input. CLKIN provides the clock signal to be distributed by the CDC536 clock-driver circuit. CLKIN is

used to provide the reference signal to the integrated phase-lock loop that generates the clock output

signals. CLKIN must have a fixed frequency and fixed phase in order for the phase-lock loop to obtain

phase lock. Once the circuit is powered up and a valid CLKIN signal is applied, a stabilization time is

required for the phase-lock loop to phase lock the feedback signal to its reference signal.

CLKIN

3

I

CLR

24

26

I

I

CLR is used for testing purposes only. Connect CLR to GND for normal operation.

Feedback input. FBIN provides the feedback signal to the internal PLL. FBIN must be hardwired to one of

the six clock outputs to provide frequency and phase lock. The internal PLL adjusts the output clocks to

obtain zero phase delay between the FBIN and differential CLKIN inputs.

FBIN

Output enable. OE is the output enable for all outputs. When OE is low, all outputs are enabled. When OE

is high, all outputs are in the high-impedance state. Since the feedback signal for the phase-lock loop is

taken directly from an output, placing the outputs in the high-impedance state interrupts the feedback loop;

therefore, when a high-to-low transition occurs at OE, enabling the output buffers, a stabilization time is

required before the phase-lock loop obtains phase lock.

OE

5

I

Output configuration select. SEL selects the output configuration for each output bank (e.g. 1×, 1/2×, or

2×).(see Tables 1 and 2).

SEL

4

I

I

TEST is used to bypass the phase-lock loop circuitry for factory testing of the device. When TEST is low,

all outputs operate using the PLL circuitry. When TEST is high, the outputs are placed in a test mode that

bypasses the PLL circuitry. TEST should be grounded for normal operation.

TEST

25

These outputs are configured by SEL to transmit one-half or one-fourth the frequency of the VCO. The

relationship between the CLKIN frequency and the output frequency is dependent on SEL. The duty cycle

of the Y output signals is nominally 50%, independent of the duty cycle of the CLKIN signal.

1Y1-1Y3

7, 10, 13

O

O

These outputs transmit one-half the frequency of the VCO. The relationship between the CLKIN frequency

and the output frequency is dependent on the frequency of the output being fed back to FBIN. The duty

cycle of the Y output signals is nominally 50% independent of the duty cycle of the CLKIN signal.

2Y1-2Y3 22, 19, 16

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)

(1)

UNIT

-0.5 V to 4.6 V

-0.5 V to 7 V

-0.5 V to 5.5 V

64 mA

Supply voltage range, VCC

(2)

Input voltage range, VI (see

)

(2)

Voltage range applied to any output in the high state or power-off state, VO(see

Current into any output in the low state, IO

Input clamp current, IIK(VI < 0)

)

-20 mA

Output clamp current, IOK(VO < 0)

-50 mA

Maximum power dissipation at TA = 55°C (in still air) (see (3)):

DB package

DL package

0.68 W

0.7 W

Operating free-air temperature range, TA

Storage temperature range, Tstg

0°C to 70°C

-65°C to 150°C

(1) Stresses beyond those listed under "absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

(3) The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 75 mils. For

more information, refer to the Package Thermal Considerations application note in the ABT Advanced BiCMOS Technology Data Book,

literature number SCBD002.

4

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]