bq3285

date period (see Figure 2). The alarm flag bit may also

be set during the update cycle.

Functional Description

The bq3285 copies the local register updates into the

user buffer accessed by the host processor. When a 1 is

written to the update transfer inhibit bit (UTI) in regis-

ter B, the user copy of the clock and calendar bytes re-

mains unchanged, while the local copy of the same bytes

continues to be updated every second.

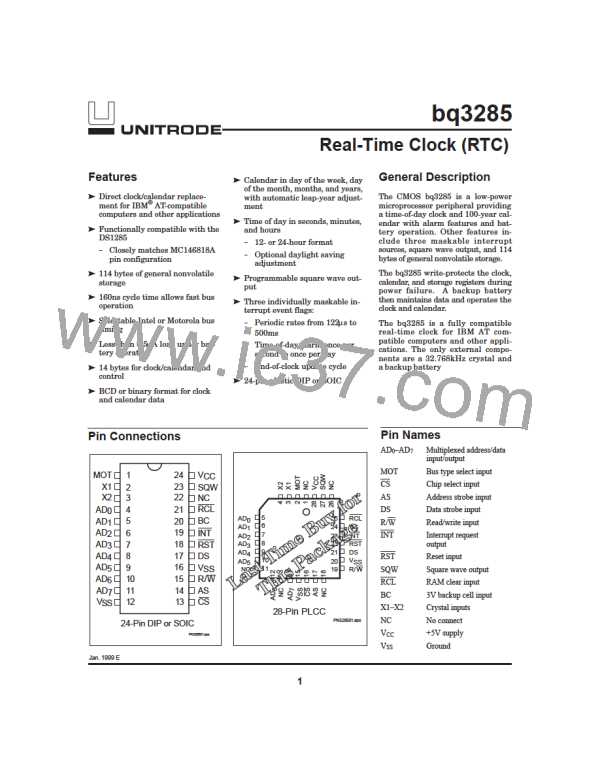

Address Map

The bq3285 provides 14 bytes of clock and control/status

registers and 114 bytes of general nonvolatile storage.

Figure 1 illustrates the address map for the bq3285.

The update-in-progress bit (UIP) in register A is set

tBUC time before the beginning of an update cycle (see

Figure 2). This bit is cleared and the update-complete

flag (UF) is set at the end of the update cycle.

Update Period

The update period for the bq3285 is one second. The

bq3285 updates the contents of the clock and calendar

locations during the update cycle at the end of each up-

0

00

0

1

2

3

Seconds

Seconds Alarm

Minutes

00

01

Clock and

Control Status

Registers

14

Bytes

13

14

0D

0E

02

03

Minutes Alarm

Hours

04

05

4

5

BCD or

Binary

Format

Hours Alarm

6

7

8

Day of Week

Day of Month

Month

06

07

08

114

Bytes

Storage

Registers

Year

09

0A

0B

9

10

11

Register A

Register B

12

13

Register C

Register D

0C

0D

127

7F

Figure 1. Address Map

Update Period

(1s)

UIP

t

(Update Cycle)

UC

tBUC

Figure 2. Update Period Timing and UIP

Jan. 1999 E

4

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]