bq20z45

SLUS800–MARCH 2009 .................................................................................................................................................................................................. www.ti.com

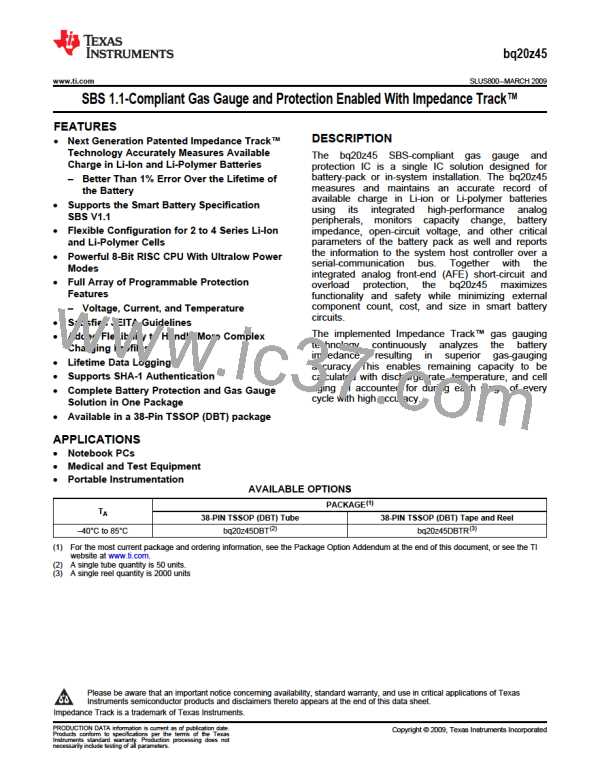

ELECTRICAL CHARACTERISTICS (continued)

over operating free-air temperature range (unless otherwise noted), TA = –40°C to 85°C, V(REG25) = 2.41 V to 2.59 V,

V(BAT) = 14 V, C(REG25) = 1 µF, C(REG33) = 2.2 µF; typical values at TA = 25°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

25

TYP

MAX UNIT

drawing current until REG33 = 3 V

short REG33 to VSS, REG33 = 0 V

100

145

mA

65

I(REG33MAX)

Current Limit

12

THERMISTOR DRIVE

V(TOUT) Output voltage

I(TOUT) = 0 mA; TA = 25°C

V(REG25)

50

V

I(TOUT) = 1 mA; RDS(on) = (V(REG25)

V(TOUT) )/ 1 mA; TA = –40°C to 100°C

-

RDS(on)

TOUT pass element resistance

100

Ω

VCELL+ HIGH VOLTAGE TRANSLATION

VC(n) - VC(n+1) = 0 V;

TA = –40°C to 100°C

0.950

0.275

0.965

0.975

0.3

1

0.375

0.985

V(VCELL+OUT)

VC(n) - VC(n+1) = 4.5 V;

TA = –40°C to 100°C

internal AFE reference voltage ;

TA = –40°C to 100°C

V(VCELL+REF)

V(VCELL+PACK)

Translation output

0.975

V

Voltage at PACK pin;

TA = –40°C to 100°C

0.98 ×

V(PACK)/18

1.02 ×

V(PACK)/18

V(PACK)/18

Voltage at BAT pin;

TA = –40°C to 100°C

0.98 ×

V(BAT)/18

V(VCELL+BAT)

CMMR

V(BAT)/18 1.02 × V(BAT)/18

Common mode rejection ratio

Cell scale factor

VCELL+

40

dB

K= {VCELL+ output (VC5=0V;

VC4=4.5V) - VCELL+ output (VC5=0V;

VC4=0V)}/4.5

0.147

0.150

0.153

0.153

K

K= {VCELL+ output (VC2=13.5V;

VC1=18V) - VCELL+ output

(VC5=13.5V; VC1=13.5V)}/4.5

0.147

12

0.150

18

VC(n) - VC(n+1) = 0V; VCELL+ = 0 V;

TA = –40°C to 100°C

I(VCELL+OUT)

Drive Current to VCELL+ capacitor

µA

CELL output (VC2 = VC1 = 18 V) -

CELL output (VC2 = VC1 = 0 V)

V(VCELL+O)

IVCnL

CELL offset error

-18

-1

-1

18

1

mV

VC(n) pin leakage current

VC1, VC2, VC3, VC4, VC5 = 3 V

0.01

µA

CELL BALANCING

R(BAL) internal cell balancing FET resistance

RDS(on) for internal FET switch at

VDS = 2 V; TA = 25°C

200

400

600

Ω

HARDWARE SHORT CIRCUIT AND OVERLOAD PROTECTION; TA = 25°C (unless otherwise noted)

VOL = 25 mV (min)

15

90

25

100

35

110

225

70

OL detection threshold voltage

accuracy

V(OL)

VOL = 100 mV; RSNS = 0, 1

VOL = 205 mV (max)

mV

mV

mV

185

30

205

V(SCC) = 50 mV (min)

50

SCC detection threshold voltage

accuracy

V(SCC)

V(SCC) = 200 mV; RSNS = 0, 1

V(SCC) = 475 mV (max)

V(SCD) = –50 mV (min)

180

428

–30

–180

–428

200

220

523

–70

–220

–523

475

–50

SCD detection threshold voltage

accuracy

V(SCD)

V(SCD) = –200 mV; RSNS = 0, 1

V(SCD) = –475 mV (max)

–200

–475

±15.25

50

tda

tpd

Delay time accuracy

µs

µs

Protection circuit propagation delay

FET DRIVE CIRCUIT; TA = 25°C (unless otherwise noted)

V(DSGON) = V(DSG) - V(PACK)

;

V(DSGON)

DSG pin output on voltage

CHG pin output on voltage

V(GS) = 10 MΩ; DSG and CHG on;

TA = –40°C to 100°C

8

8

12

12

16

16

V

V

V(CHGON) = V(CHG) - V(BAT)

;

V(CHGON)

V(GS) = 10 MΩ; DSG and CHG on;

TA = –40°C to 100°C

V(DSGOFF)

V(CHGOFF)

DSG pin output off voltage

CHG pin output off voltage

V(DSGOFF) = V(DSG) - V(PACK)

V(CHGOFF) = V(CHG) - V(BAT)

0.2

0.2

V

V

6

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated

Product Folder Link(s): bq20z45

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]