AM6548, AM6528, AM6526

ZHCSLA7B –DECEMBER 2019 –REVISED JUNE 2021

www.ti.com.cn

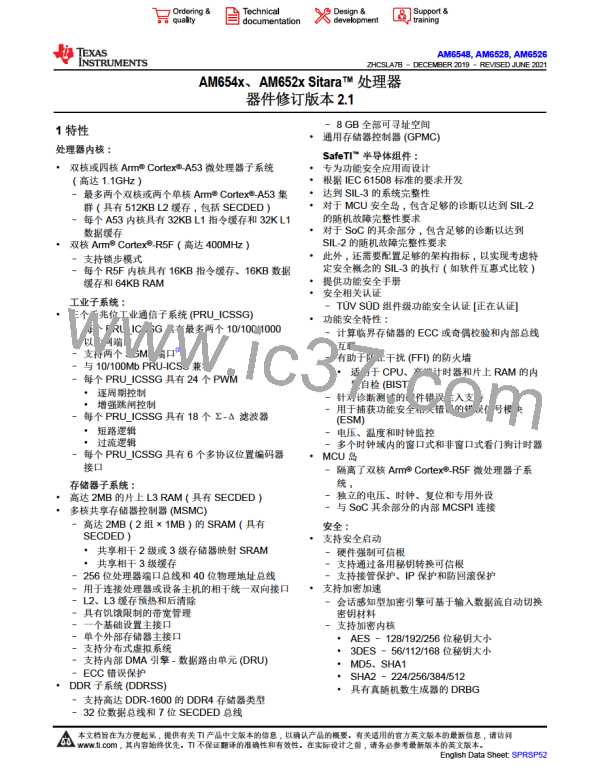

6.3.21 PRU_ICSSG

6.3.21.1 MAIN Domain

Note

The PRU_ICSSG contains a second layer of multiplexing to enable additional functionality on the PRU

GPO and GPI signals. This internal wrapper multiplexing is described in the PRU_ICSSG chapter in

the device TRM.

表6-53. PRU_ICSSG0 Signal Descriptions

PIN TYPE

SIGNAL NAME [1]

DESCRIPTION [2]

BALL [4]

[3]

PRU_ICSSG Enhanced Capture (ECAP) Input or

Auxiliary PWM (APWM) Ouput

PRG0_ECAP0_IN_APWM_OUT

IO

V25

PRG0_ECAP0_SYNC_IN

PRU_ICSSG ECAP Sync Input

I

U27

U26

PRG0_ECAP0_SYNC_OUT

PRG0_IEP0_EDIO_OUTVALID

PRU_ICSSG ECAP Sync Output

O

O

PRU_ICSSG Industrial Ethernet Digital I/O Outvalid

AD12

PRU_ICSSG Industrial Ethernet Distributed Clock Latch

Input

PRG0_IEP0_EDC_LATCH_IN0

PRG0_IEP0_EDC_LATCH_IN1

PRG0_IEP0_EDC_SYNC_OUT0

PRG0_IEP0_EDC_SYNC_OUT1

PRG0_IEP0_EDIO_DATA_IN_OUT28

PRG0_IEP0_EDIO_DATA_IN_OUT29

PRG0_IEP0_EDIO_DATA_IN_OUT30

PRG0_IEP0_EDIO_DATA_IN_OUT31

PRG0_IEP1_EDC_LATCH_IN0

PRG0_IEP1_EDC_LATCH_IN1

PRG0_IEP1_EDC_SYNC_OUT0

PRG0_IEP1_EDC_SYNC_OUT1

I

V25

U27

U24

U26

V26

U25

Y28

AA28

Y26

W28

W26

Y27

PRU_ICSSG Industrial Ethernet Distributed Clock Latch

Input

I

PRU_ICSSG Industrial Ethernet Distributed Clock Sync

Output

O

O

IO

IO

IO

IO

I

PRU_ICSSG Industrial Ethernet Distributed Clock Sync

Output

PRU_ICSSG Industrial Ethernet Digital I/O Data Input/

Output

PRU_ICSSG Industrial Ethernet Digital I/O Data Input/

Output

PRU_ICSSG Industrial Ethernet Digital I/O Data Input/

Output

PRU_ICSSG Industrial Ethernet Digital I/O Data Input/

Output

PRU_ICSSG Industrial Ethernet Distributed Clock Latch

Input

PRU_ICSSG Industrial Ethernet Distributed Clock Latch

Input

I

PRU_ICSSG Industrial Ethernet Distributed Clock Sync

Output

O

O

PRU_ICSSG Industrial Ethernet Distributed Clock Sync

Output

PRG0_MDIO0_MDC

PRG0_MDIO0_MDIO

PRG0_PRU0_GPI0

PRG0_PRU0_GPI1

PRG0_PRU0_GPI2

PRG0_PRU0_GPI3

PRG0_PRU0_GPI4

PRG0_PRU0_GPI5

PRG0_PRU0_GPI6

PRG0_PRU0_GPI7

PRG0_PRU0_GPI8

PRG0_PRU0_GPI9

PRU_ICSSG MDIO Clock

O

AE28

AE26

V24

PRU_ICSSG MDIO Data

IO

I

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

PRU_ICSSG PRU Data Input

I

W25

W24

AA27

Y24

I

I

I

I

V28

I

Y25

I

U27

V27

I

I

V26

Copyright © 2021 Texas Instruments Incorporated

88

Submit Document Feedback

Product Folder Links: AM6548 AM6528 AM6526

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]