ADS1299

SBAS499A –JULY 2012–REVISED AUGUST 2012

www.ti.com

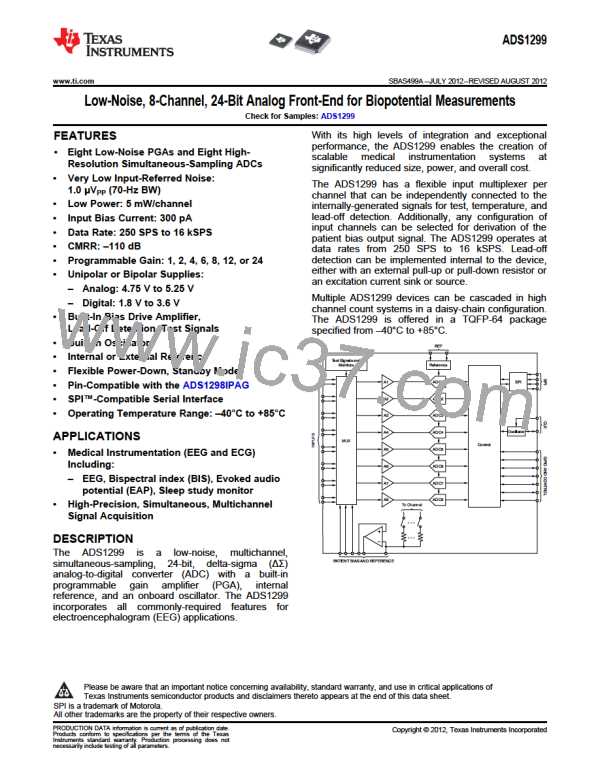

TIMING CHARACTERISTICS

tCLK

CLK

tCSSC

tCSH

tSDECODE

tSPWL

CS

tSCCS

tSCLK

tSPWH

SCLK

1

2

3

8

1

2

3

8

tDIHD

tDOHD

tDIST

tDOPD

DIN

tCSDOZ

Hi-Z

tCSDOD

Hi-Z

DOUT

NOTE: SPI settings are CPOL = 0 and CPHA = 1.

Figure 1. Serial Interface Timing

tDISCK2ST

tDISCK2HT

MSBD1

LSBD1

DAISY_IN

SCLK

1

2

3

216

217

218

219

MSBD1

MSB

LSB

DOUT

Figure 2. Daisy-Chain Interface Timing

Timing Requirements For Figure 1 and Figure 2(1)

2.7 V ≤ DVDD ≤ 3.6 V

1.8 V ≤ DVDD ≤ 2 V

PARAMETER

tCLK

DESCRIPTION

MIN

444

6

TYP

MAX

MIN

444

17

TYP

MAX UNIT

Master clock period

666

666

ns

ns

tCSSC

CS low to first SCLK, setup time

SCLK period

tSCLK

50

15

10

10

10

66.6

25

ns

tSPWH, L

tDIST

SCLK pulse width, high and low

DIN valid to SCLK falling edge: setup time

Valid DIN after SCLK falling edge: hold time

SCLK falling edge to invalid DOUT: hold time

SCLK rising edge to DOUT valid: setup time

CS high pulse

ns

10

ns

tDIHD

11

ns

tDOHD

10

ns

tDOPD

17

10

32

20

ns

tCSH

2

10

4

2

20

4

tCLKs

ns

tCSDOD

tSCCS

CS low to DOUT driven

Eighth SCLK falling edge to CS high

Command decode time

tCLKs

tCLKs

ns

tSDECODE

tCSDOZ

tDISCK2ST

tDISCK2HT

4

4

CS high to DOUT Hi-Z

Valid DAISY_IN to SCLK rising edge: setup time

Valid DAISY_IN after SCLK rising edge: hold time

10

10

10

10

ns

ns

(1) Specifications apply from –40°C to +85°C. Load on DOUT = 20 pF || 100 kΩ.

8

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): ADS1299

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]