STM32F105xx, STM32F107xx

Electrical characteristics

5.3.17

DAC electrical specifications

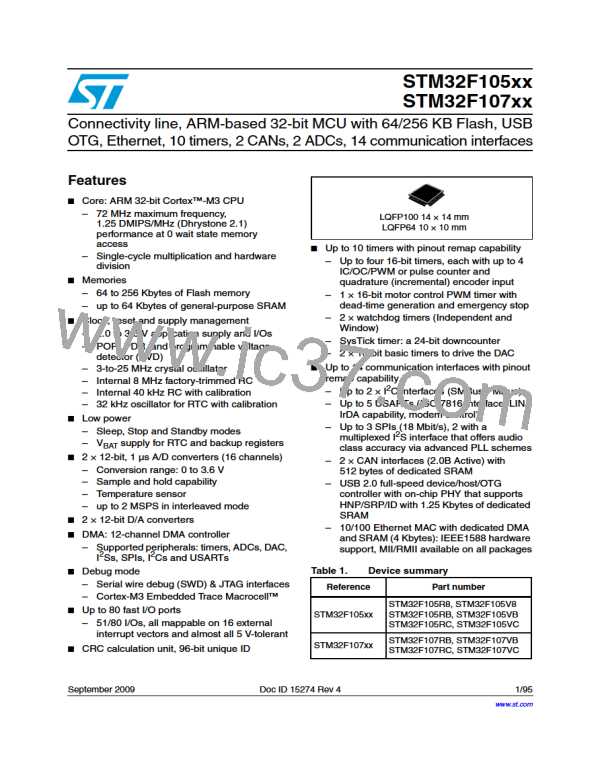

Table 55. DAC characteristics

Symbol

VDDA

Parameter

Min

Typ

Max

Unit

Comments

Analog supply voltage

2.4

3.6

V

VREF+

VSSA

Reference supply voltage

Ground

2.4

0

3.6

0

V

V

VREF+ must always be below VDDA

(1)

RLOAD

Resistive load with buffer ON

5

kY

When the buffer is OFF, the

Minimum resistive load between

DAC_OUT and VSS to have a 1%

accuracy is 1.5 MY

Impedance output with buffer

OFF

(1)

RO

15

50

kY

Maximum capacitive load at

pF DAC_OUT pin (when the buffer is

ON).

(1)

CLOAD

Capacitive load

It gives the maximum output

DAC_OUT Lower DAC_OUT voltage

min(1)

with buffer ON

excursion of the DAC.

V

It corresponds to 12-bit input code

0.2

(0x0E0) to (0xF1C) at VREF+

=

DAC_OUT Higher DAC_OUT voltage

max(1)

with buffer ON

3.6 V and (0x155) to (0xEAB) at

VREF+ = 2.4 V

VDDA – 0.2

V

mV

V

DAC_OUT Lower DAC_OUT voltage

min(1)

with buffer OFF

0.5

It gives the maximum output

excursion of the DAC.

DAC_OUT Higher DAC_OUT voltage

max(1)

VREF+ – 1LSB

with buffer OFF

DAC DC current consumption

in quiescent mode (Standby

mode)

With no load, worst code (0xF1C)

µA at VREF+ = 3.6 V in terms of DC

consumption on the inputs

IDDVREF+

220

380

480

With no load, middle code (0x800)

on the inputs

µA

DAC DC current consumption

in quiescent mode (Standby

mode)

IDDA

With no load, worst code (0xF1C)

µA at VREF+ = 3.6 V in terms of DC

consumption on the inputs

Given for the DAC in 10-bit

configuration.

0.5

LSB

Differential non linearity

Difference between two

consecutive code-1LSB)

DNL(2)

Given for the DAC in 12-bit

configuration.

2

1

LSB

Integral non linearity

(difference between

Given for the DAC in 10-bit

configuration.

LSB

measured value at Code i

and the value at Code i on a

line drawn between Code 0

and last Code 1023)

INL(2)

Given for the DAC in 12-bit

configuration.

4

LSB

Doc ID 15274 Rev 4

73/95

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]