16 Mbit Concurrent SuperFlash + 2 / 4 Mbit SRAM ComboMemory

SST34HF1621 / SST34HF1641

Data Sheet

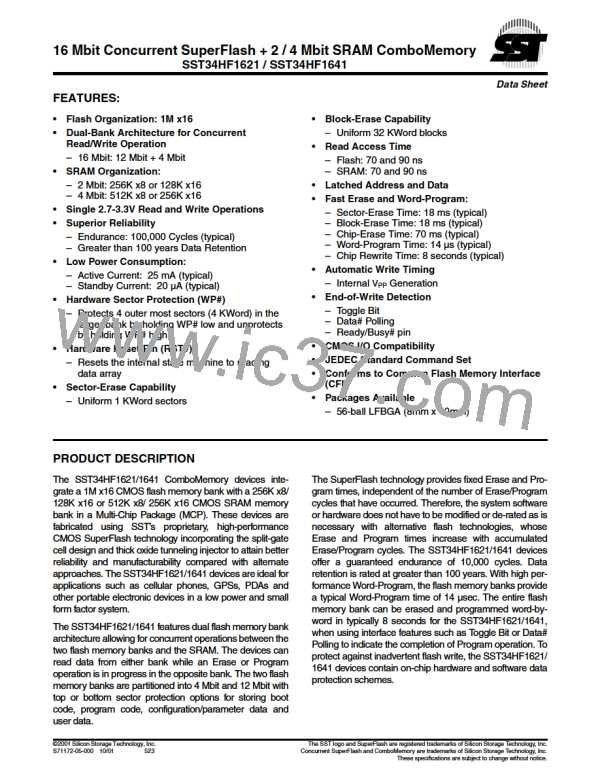

T

BE

SIX-BYTE CODE FOR BLOCK-ERASE

5555 5555 2AAA

ADDRESS A

5555

2AAA

BA

19-0

X

BEF#

OE#

T

WP

WE#

T

BR

T

BY

RY/BY#

DQ

15-0

XXAA

SW0

XX55

SW1

XX80

SW2

XXAA

SW3

XX55

SW4

XX50

SW5

VALID

523 ILL F10.4

Note: This device also supports BEF# controlled Block-Erase operation. The WE# and BEF#

signals are interchageable as long as minimum timings are met. (See Table 15)

BA = Block Address

X

X can be V or V , but no other value.

IL IH

FIGURE 12: FLASH WE# CONTROLLED BLOCK-ERASE TIMING DIAGRAM

T

SE

SIX-BYTE CODE FOR SECTOR-ERASE

5555

2AAA

5555

5555

2AAA

SA

ADDRESS A

X

19-0

BEF#

OE#

T

WP

WE#

T

BR

T

BY

RY/BY#

DQ

15-0

XXAA

SW0

XX55

SW1

XX80

SW2

XXAA

SW3

XX55

SW4

XX30

SW5

VALID

523 ILL F11.4

Note: This device also supports BEF# controlled Sector-Erase operation. The WE# and BEF#

signals are interchageable as long as minimum timings are met. (See Table 15)

SA = Sector Address

X

X can be V or V , but no other value.

IL IH

FIGURE 13: FLASH WE# CONTROLLED SECTOR-ERASE TIMING DIAGRAM

©2001 Silicon Storage Technology, Inc.

S71172-05-000 10/01 523

21

SST [ SILICON STORAGE TECHNOLOGY, INC ]

SST [ SILICON STORAGE TECHNOLOGY, INC ]