ST7735

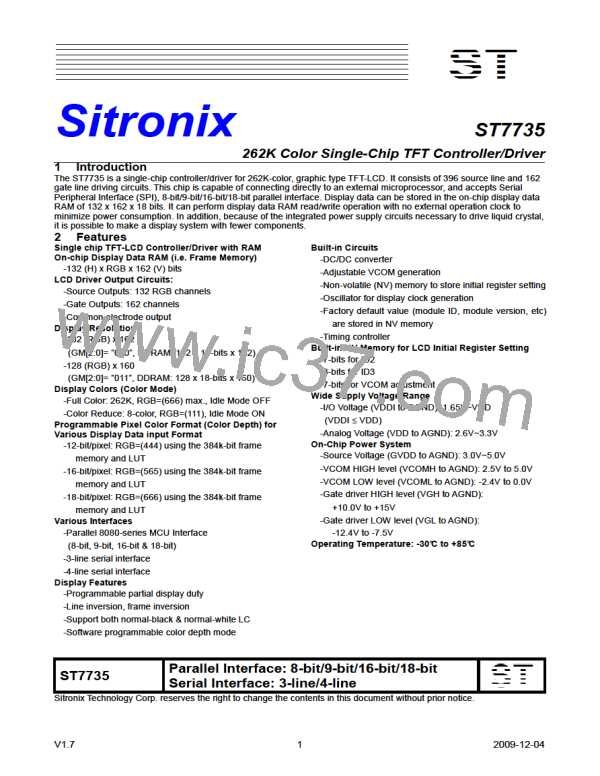

9.2.1 Write cycle sequence

The write cycle means that the host writes information (command or/and data) to the display via the interface. Each write

cycle (WRX high-low-high sequence) consists of 3 control signals (D/CX, RDX, WRX) and data signals (D[17:0]). D/CX bit

is a control signal, which tells if the data is a command or a data. The data signals are the command if the control signal is

low (=’0’) and vice versa it is data (=’1’).

WRX

D[17:0]

The host stops to

control D[17:0] lines.

The host starts to control D[17:0]

lines when there is a falling edge

of the WRX.

The display writes D[17:0] lines

when there is a rising edge of

WRX.

Fig. 9.2.1 8080-series WRX protocol

Note: WRX is an unsynchronized signal (It can be stopped).

1ꢀbyteꢁ

2ꢀbyteꢁ

Nꢀbyteꢁ

command

command

command

D[17:0]

RESX

CSX

S

CMD

CMD

PA1

CMD

PA1

PANꢀ2

PANꢀ1

P

“1”

D/CX

RDX

“1”

WRX

D[17:0]

S

S

CMD

CMD

CMD

PA1

PA1

CMD

CMD

PA1

PA1

PANꢀ2

PANꢀ1

P

P

HostꢁD[17:0]

HostꢁtoꢁLCD

CMD

HiꢀZ

PANꢀ2

PANꢀ1

DriverꢁD[17:0]

LCDꢁtoꢁHost

SignalsꢁonꢁD[17:0],ꢁD/CX,ꢁR/WX,ꢁEꢁ

pinsꢁduringꢁCSX=1ꢁareꢁignored.

CMD:ꢁwriteꢁcommandꢁcode

PA:ꢁparameterꢁorꢁdisplayꢁdata

Fig. 9.2.2 8080-series parallel bus protocol, write to register or display RAM

V1.7

27

2009-12-04

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]