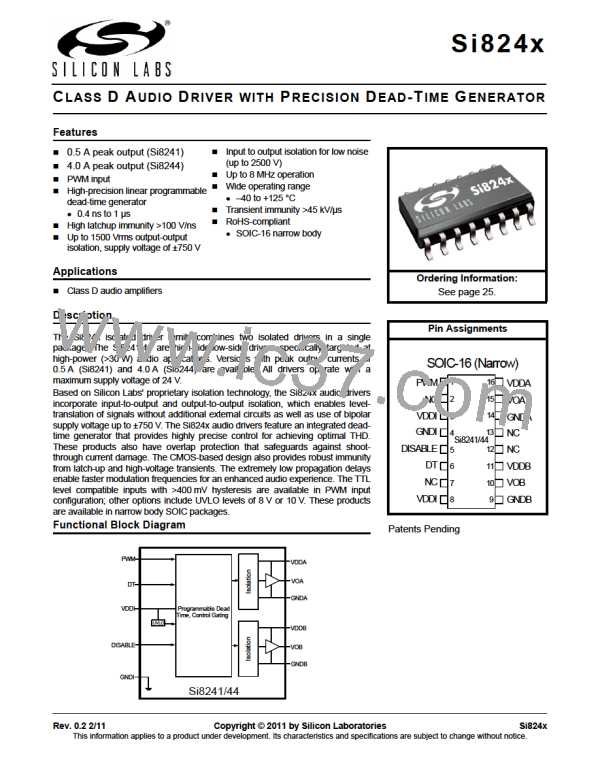

Si824x

3.8. Programmable Dead Time and Overlap Protection

All high-side/low-side drivers (Si8241/4) include programmable overlap protection to prevent outputs VOA and

VOB from being high at the same time. These devices also include programmable dead time, which adds a user-

programmable delay between transitions of VOA and VOB. When enabled, dead time is present on all transitions,

even after overlap recovery. The amount of dead time delay (DT) is programmed by a single resistor (RDT)

connected from the DT input to ground per Equation 5. Minimum dead time (approximately 400 ps) can be

achieved by connecting the DT pin to VDDI. Note that dead time accuracy is limited by the resistor’s (R

)

DT

tolerance and temperature coefficient. See Figures 36 and 37 for additional information about dead time operation.

DT 10 RDT

where:

DT= dead time (ns)

and

RDT= dead time programming resistor (k

Equation 5.

1000

900

800

700

600

500

400

300

200

100

0

0

20

40

60

80

100

Dead-time Resistance (kꢀ)

Figure 36. Dead Time vs.Resistance (RDT)

100

90

80

70

60

50

40

30

20

10

0

RDT = 10k

RDT = 6k

RDT = 5k

RDT = 4k

RDT = 3k

RDT = 2k

RDT = 1k

RDT = 0

-40

-20

0

20

40

60

80

100 120

Temperature (°C)

Figure 37. Dead Time vs.Temperature

22

Rev. 0.2