EFR32MG13 Mighty Gecko Multi-Protocol Wireless SoC Family Data Sheet

Electrical Specifications

SPI Slave Timing

Table 4.59. SPI Slave Timing

Parameter

Symbol

Test Condition

Min

Typ

Max

Unit

SCLK period 1 2 3

tSCLK

6 *

tHFPERCLK

—

—

ns

SCLK high time1 2 3

SCLK low time1 2 3

tSCLK_HI

2.5 *

tHFPERCLK

—

—

—

—

ns

ns

tSCLK_LO

2.5 *

tHFPERCLK

CS active to MISO 1 2

CS disable to MISO 1 2

MOSI setup time 1 2

MOSI hold time 1 2 3

SCLK to MISO 1 2 3

tCS_ACT_MI

tCS_DIS_MI

tSU_MO

4

4

—

—

—

—

—

70

50

—

—

ns

ns

ns

ns

ns

12.5

13

tH_MO

tSCLK_MI

6 + 1.5 *

tHFPERCLK

45 + 2.5 *

tHFPERCLK

Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2. Measurement done with 8 pF output loading at 10% and 90% of VDD (figure shows 50% of VDD).

3. tHFPERCLK is one period of the selected HFPERCLK.

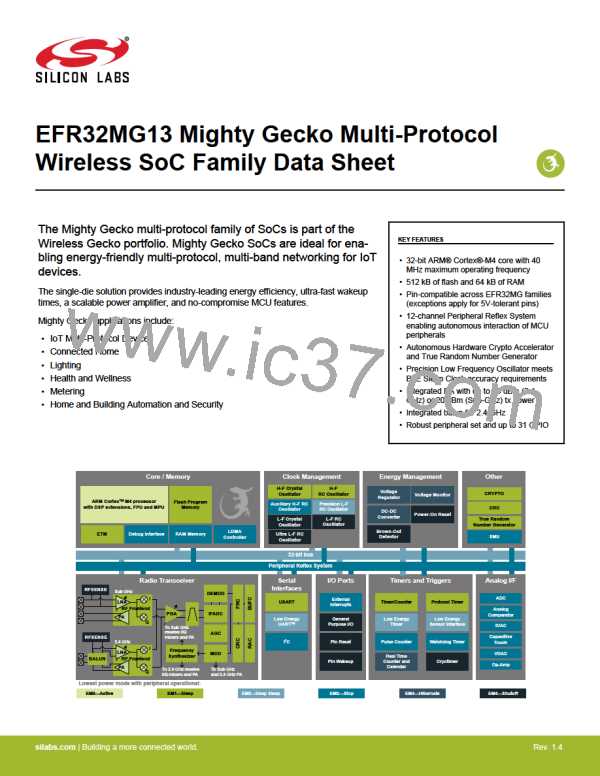

tCS_ACT_MI

CS

tCS_DIS_MI

SCLK

CLKPOL = 0

tSCLK_HI

tSCLK_LO

SCLK

tSU_MO

CLKPOL = 1

tSCLK

tH_MO

MOSI

MISO

tSCLK_MI

Figure 4.2. SPI Slave Timing Diagram

4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

silabs.com | Building a more connected world.

Rev. 1.4 | 112