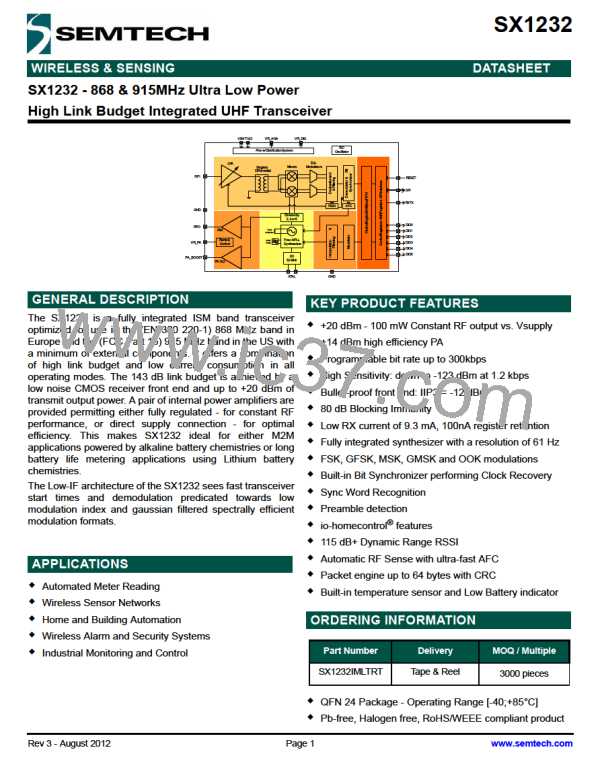

SX1232

WIRELESS & SENSING

DATASHEET

Name

(Address)

Default

value

Bits

Mode

Variable Name

Description

RegAfcMsb

(0x1b)

7-0

7-0

7-0

7-0

AfcValue(15:8)

AfcValue(7:0)

FeiValue(15:8)

FeiValue(7:0)

rw

0x00 MSB of the AfcValue, 2’s complement format. Can be used to

overwrite the current AFC value

RegAfcLsb

(0x1c)

rw

rw

rw

0x00 LSB of the AfcValue, 2’s complement format. Can be used to

overwrite the current AFC value

RegFeiMsb

(0x1d)

-

MSB of the measured frequency offset, 2’s complement. Must

be read before RegFeiLsb.

RegFeiLsb

(0x1e)

-

LSB of the measured frequency offset, 2’s complement

Frequency error = FeiValue x Fstep

RegPreambleDete

7

PreambleDetectorOn

rw

0x01 Enables Preamble detector when set to 1. The AGC settings

ct

(0x1f)

*

supersede this bit during the startup / AGC phase.

0 Æ Turned off

1 Æ Turned on

6-5

PreambleDetectorSize

rw

0x01 Number of Preamble bytes to detect to trigger an interrupt

*

00 Æ 1 byte

01 Æ 2 bytes

10 Æ 3 bytes

11 Æ Reserved

4-0

7-0

PreambleDetectorTol

TimeoutRxRssi

rw

rw

0x0A Number or chip errors tolerated over PreambleDetectorSize.

*

4 chips per bit.

RegRxTimeout1

(0x20)

0x00

Timeout interrupt is generated TimeoutRxRssi*16*Tbit after

switching to Rx mode if Rssi interrupt doesn’t occur (i.e.

RssiValue > RssiThreshold)

0x00: TimeoutRxRssi is disabled

RegRxTimeout2

(0x21)

7-0

7-0

TimeoutRxPreamble

TimeoutSignalSync

rw

rw

0x00

0x00

Timeout interrupt is generated TimeoutRxPreamble*16*Tbit

after switching to Rx mode if Preamble interrupt doesn’t occur

0x00: TimeoutRxPreamble is disabled

RegRxTimeout3

(0x22)

Timeout interrupt is generated TimeoutSignalSync*16*Tbit

after the Rx mode is programmed, if SyncAddress doesn’t

occur

0x00: TimeoutSignalSync is disabled

RegRxDelay

(0x23)

7-0

InterPacketRxDelay

rw

0x00 Additional delay befopre an automatic receiver restart is

launched:

Delay = InterPacketRxDelay*4*Tbit

RC Oscillator registers

RegOsc

(0x24)

7-4

3

unused

r

-

unused

RcCalStart

wt

0x00 Triggers the calibration of the RC oscillator when set. Always

reads 0. RC calibration must be triggered in Standby mode.

2-0

ClkOut

rw

0x07

*

Selects CLKOUT frequency:

000 Æ FXOSC

001 Æ FXOSC / 2

010 Æ FXOSC / 4

011 Æ FXOSC / 8

100 Æ FXOSC / 16

101 Æ FXOSC / 32

110 Æ RC (automatically enabled)

111 Æ OFF

Rev 3 - August 2012

Page 72

www.semtech.com

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]