3858 Group

t

C(CNTR)

t

WL(CNTR)

t

WH(CNTR)

CNTR

CNTR

0

1

0.8VCC

0.2VCC

0.2VCC

t

WL(INT)

t

WH(INT)

0.8VCC

INT

0

to INT

3

t

W(RESET)

0.8VCC

RESET

0.2VCC

t

C(XIN)

t

WL(XIN)

t

WH(XIN)

0.8VCC

X

IN

0.2VCC

t

C(SCLK1),

t

C(SCLK2)

t

WL(SCLK1),

t

WL(SCLK2

)

t

WH(SCLK1), WH(SCLK2)

t

t

r

t

f

S

S

CLK1

CLK2

0.8VCC

0.2VCC

t

t

h(SCLK1

h(SCLK2

-

-

RxD),

t

t

su(R

x

D

-

S

CLK1),

CLK2

S

IN2)

su(SIN2

-

S

)

R D

X

IN2

0.8V

0.2VCCCC

S

t

t

d(SCLK1-TXD),

t

t

v(SCLK1-T

XD),

d(SCLK2-SOUT2

)

v(SCLK2-SOUT2

)

T D

X

S

OUT2

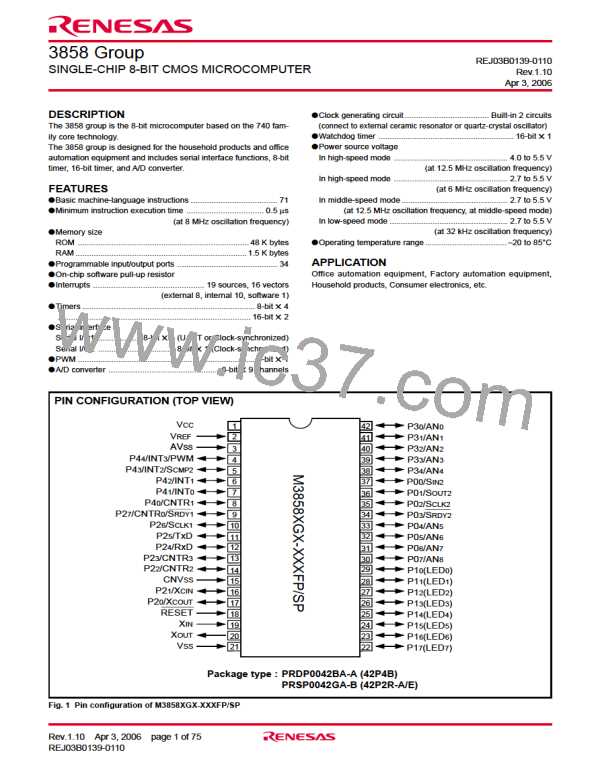

Fig. 62 Timing diagram

Rev.1.10 Apr 3, 2006 page 68 of 75

REJ03B0139-0110

RENESAS [ RENESAS TECHNOLOGY CORP ]

RENESAS [ RENESAS TECHNOLOGY CORP ]