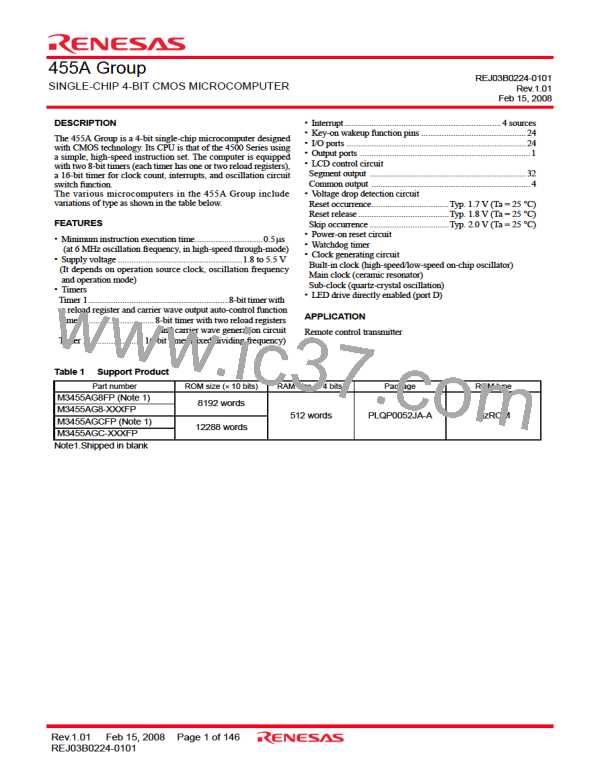

455A Group

MR3, MR2

11

Division circuit

Divided by 8

Divided by 4

Divided by 2

System clock (STCK)

MR1, MR0

00

10

High-speed on-chip oscillator

Internal clock

generating circuit

(divided by 3)

Instruction clock

(INSTCK)

01

00

01

10

XIN

Ceramic resonance

Quartz-crystal

oscillation

XCIN

11

Low-speed on-chip oscillator

Prescaler (8)

ORCLK

PA0

Reload register RPS (8)

(TPSAB)

(TPSAB)

(TPSAB)

(TABPS)

(TABPS)

Register B Register A

I12

0

I11

0

One-sided edge

detection circuit

I10

D5/INT

I13

S

R

Q

1

Both edges

detection circuit

1

1

0

I10

W13

T1UDF

Timer 1

interrupt

Timer 1 (8)

T1F

W11, W10

00

Timer 1 underflow signal

(T1UDF)

PWMOUT

ORCLK

T3UDF

Reload register R1 (8)

01

(T1AB)

(T1AB)

(TR1AB)

(T1AB)

10

11

(TAB1)

(TAB1)

Register B Register A

W40

0

C/CNTR

W12

1

PWMOUT

Port C output

T1UDF

W41

D

T

W11 W10

Q

R

W12

Register B Register A

Q

T

PWMOD

(T2HAB)

Reload register R2H (8)

R

W20

0

Reload control circuit

W22

1

W23

T2F

XIN

“H” interval

expansion

Timer 2 (8)

Timer 2

interrupt

1

ORCLK

1/2

0

(T2R2L)

Reload register R2L (8)

W21

(T2AB)

(T2AB)

(T2AB)

(TAB2)

(TAB2)

Register B Register A

Data is set automatically from each reload register

when timer underflows (auto-reload function).

Fig 33. Timers structure (1)

Rev.1.01 Feb 15, 2008 Page 32 of 146

REJ03B0224-0101

RENESAS [ RENESAS TECHNOLOGY CORP ]

RENESAS [ RENESAS TECHNOLOGY CORP ]