PE43704

Product Specification

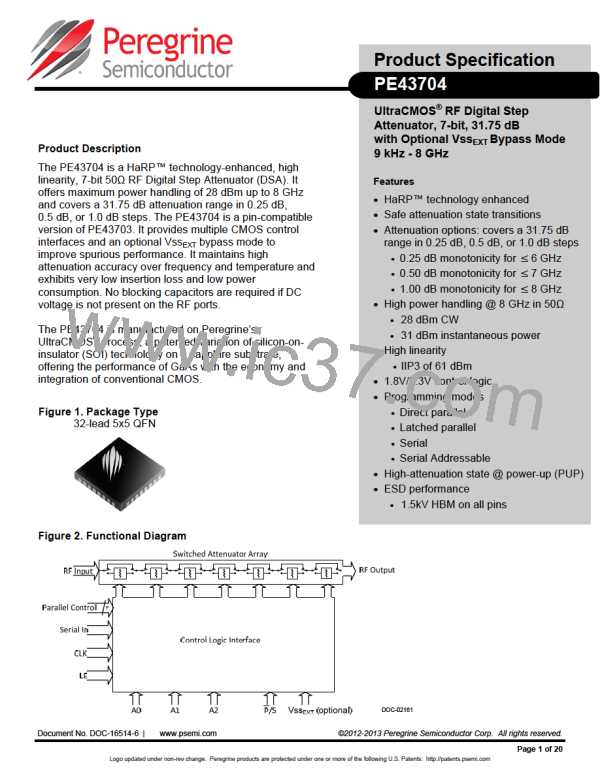

Typical Performance Data @ 25°C and VDD = 3.4V unless otherwise specified

Figure 24. Relative Phase Error vs.

Attenuation Setting

Figure 25. Relative Phase Error for 31.75 dB

Attenuation Setting vs. Frequency

70

60

50

40

30

20

10

0

100

80

60

40

20

0

0dB

0.9GHz

1.8GHz

2GHz

0.25dB

0.5dB

1dB

3GHz

4GHz

2dB

5GHz

4dB

6GHz

8dB

16dB

31.75dB

0

1

2

3

4

5

6

7

8

‐40

25

85

Frequency (GHz)

Temperature (deg C)

Figure 26. Attenuation Error @ 900 MHz vs.

Temperature

Figure 27. Attenuation Error @ 1800 MHz vs.

Temperature

0.75

0.5

0.25

0

0.5

‐40C

‐40C

25C

85C

0.25

0

25C

85C

‐0.25

‐0.5

‐0.25

‐0.5

0

4

8

12

16

20

24

28

32

0

4

8

12

16

20

24

28

32

Attenuation Setting (dB)

Attenuation Setting (dB)

Figure 28. Attenuation Error @ 3000 MHz vs.

Temperature

Figure 29. IIP3 vs. Attenuation Setting

0.75

74

72

70

68

66

64

62

60

0.5

‐40C

0.25

0

0dB

25C

85C

8dB

16dB

‐0.25

‐0.5

0

4

8

12

16

20

24

28

32

2

3

4

5

6

7

8

Attenuation Setting (dB)

Frequency (GHz)

©2012-2013 Peregrine Semiconductor Corp. All rights reserved.

Document No. DOC-16514-6 |

UltraCMOS® RFIC Solutions

Page 16 of 20

Logo updated under non-rev change. Peregrine products are protected under one or more of the following U.S. Patents: http://patents.psemi.com

PSEMI [ Peregrine Semiconductor ]

PSEMI [ Peregrine Semiconductor ]