PDIUSBD12

USB interface device with parallel bus

Philips Semiconductors

t

t

t

RHCH

CLRL

t

CLWL

WHCH

CS_N

DMACK_N

t

t

AVRL

t

AVWL

WHAX

COMMAND = 1, DATA = 0

A0

t

t

WC

WL

WR_N

t

(WC - WD)

t

(WC - RD)

t

t

WDH

WDSU

VALID DATA

DATA[7:0]

RD_N

t

RL

t

RC

t

RHNDV

t

t

RHDZ

RLDD

DATA[7:0]

VALID DATA

VALID DATA

t

RLDD

004aaa058

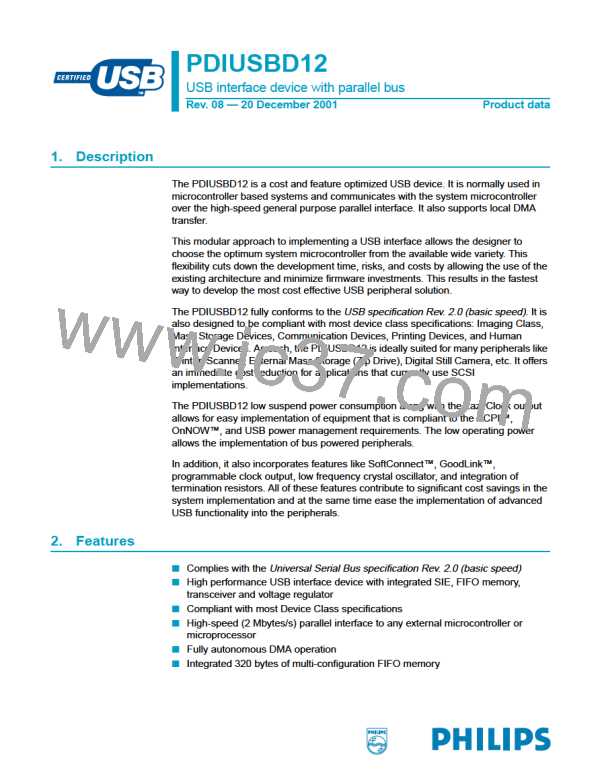

Fig 18. Parallel interface timing (I/O and DMA).

Table 18: AC characteristics (DMA)

Symbol Parameter

Conditions

Min

Max

Unit

Single-cycle DMA timings

tAHRH

tSHAH

tRHSH

tEL

DMACK_N HIGH to DMREQ HIGH time

RD_N/WR_N HIGH to DMACK_N HIGH time

DMREQ HIGH to RD_N/WR HIGH time

EOT_N LOW pulse width

−

330

ns

ns

ns

ns

130

120

10

−

−

-

simultaneous DMACK_N,

RD_N/WR_N and EOT_N

LOW time

Burst DMA timings

tSLRL

RD_N/WR_N LOW to DMREQ LOW time

-

40

ns

ns

tRHNDV RD_N (only) HIGH to next data valid

−

420

EOT timings

tELRL

EOT_N LOW to DMREQ LOW time

−

40

ns

9397 750 09238

© Koninklijke Philips Electronics N.V. 2001. All rights reserved.

Product data

Rev. 08 — 20 December 2001

26 of 35

NXP [ NXP ]

NXP [ NXP ]