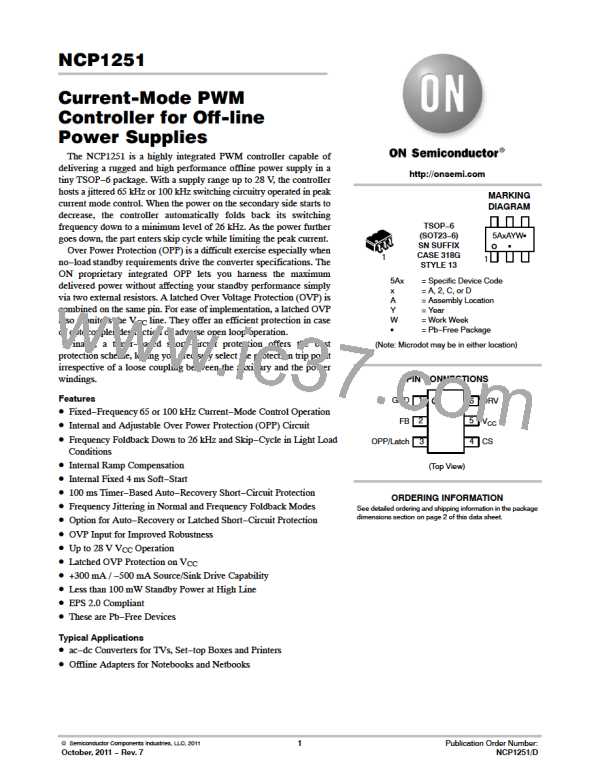

NCP1251

IpFlag

BO

OPP

600−ns time

constant

Vcc logic

UVLO

management

and fault timer

Up counter

RST

Vlatch

vdd

OVP

gone?

4

20us time

constant

VOVP

power

on reset

S

R

Q

Q

Rlimit

Vcc

Iscr

1−us

blanking

vdd

Power on

reset

65 kHz

100 kHz

clock

Clamp

Frequency

modulation

S

R

Q

Q

Frequency

foldback

Drv

Vfold

Vskip

Rramp

4 ms

SS

IpFlag

vdd

The soft−start is activated during:

− the startup sequence

− the auto−recovery burst mode

RFB

/ 4.2

VFB < 1.05 V ? setpoint = 250 mV

FB

CS

VOPP

Vlimit + VOPP

+

250 mV

peak current

freeze

GND

LEB

Vlimit

Figure 2. Internal Circuit Architecture

http://onsemi.com

3

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]