MC34152, MC33152, NCV33152

80

60

40

80

V

= 12 V

CC

V

V

= 12 V

= 0 V to 5.0 V

CC

Both Logic Inputs Driven

0 V to 5.0 V

50% Duty Cycle

IN

T = 25°C

A

60

40

Both Drive Outputs Loaded

T = 25°C

f = 200 kHz

A

f = 500 kHz

t

f

20

0

20

0

f = 50 kHz

t

r

0.1

1.0

C , OUTPUT LOAD CAPACITANCE (nF)

10

0.1

1.0

10

C , OUTPUT LOAD CAPACITANCE (nF)

L

L

Figure 13. Drive Output Rise and Fall Time

versus Load Capacitance

Figure 14. Supply Current versus Drive

Output Load Capacitance

80

60

40

8.0

6.0

4.0

2.0

T = 25°C

A

Both Logic Inputs Driven

0 V to 5.0 V,

50% Duty Cycle

Both Drive Outputs Loaded

1

Logic Inputs at V

CC

High State Drive Outputs

2

T = 25°C

A

3

1 - V = 18 V, C = 2.5 nF

CC L

2 - V = 12 V, C = 2.5 nF

CC L

3 - V = 18 V, C = 1.0 nF

CC L

4 - V = 12 V, C = 1.0 nF

4

Logic Inputs Grounded

Low State Drive Outputs

CC

L

20

0

0

10 k

100

f, INPUT FREQUENCY (Hz)

1.0 M

0

4.0

8.0

, SUPPLY VOLTAGE (V)

12

16

V

CC

Figure 15. Supply Current versus Input Frequency

Figure 16. Supply Current versus Supply Voltage

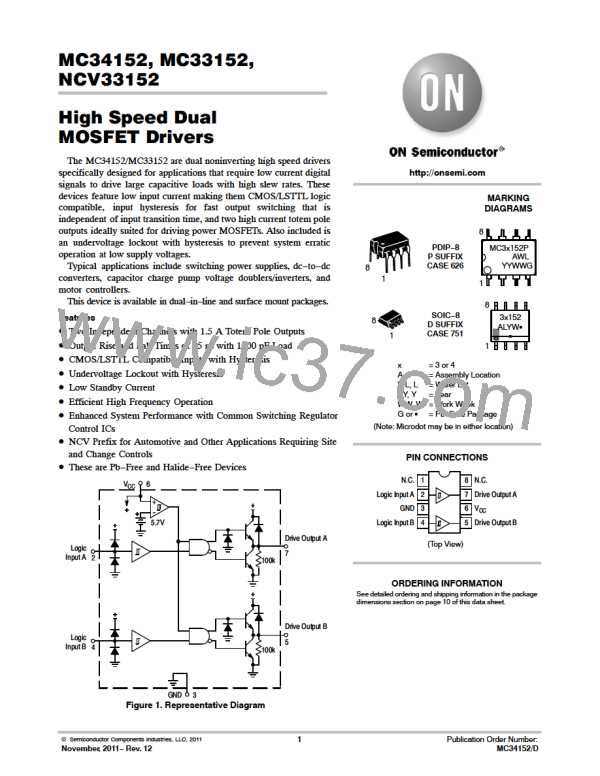

APPLICATIONS INFORMATION

Output Stage

Description

The MC34152 is a dual noninverting high speed driver

specifically designed to interface low current digital

circuitry with power MOSFETs. This device is constructed

with Schottky clamped Bipolar Analog technology which

offers a high degree of performance and ruggedness in

hostile industrial environments.

Each totem pole Drive Output is capable of sourcing and

sinking up to 1.5 A with a typical ‘on’ resistance of 2.4 W

at 1.0 A. The low ‘on’ resistance allows high output

currents to be attained at a lower V

than with

CC

comparative CMOS drivers. Each output has a 100 kW

pulldown resistor to keep the MOSFET gate low when V

CC

is less than 1.4 V. No over current or thermal protection has

Input Stage

been designed into the device, so output shorting to V or

CC

The Logic Inputs have 170 mV of hysteresis with the

input threshold centered at 1.67 V. The input thresholds are

insensitive to V making this device directly compatible

with CMOS and LSTTL logic families over its entire

operating voltage range. Input hysteresis provides fast

output switching that is independent of the input signal

transition time, preventing output oscillations as the input

thresholds are crossed. The inputs are designed to accept a

ground must be avoided.

Parasitic inductance in series with the load will cause the

CC

driver outputs to ring above V

during the turn−on

CC

transition, and below ground during the turn−off transition.

With CMOS drivers, this mode of operation can cause a

destructive output latchup condition. The MC34152 is

immune to output latchup. The Drive Outputs contain an

internal diode to V

for clamping positive voltage

CC

signal amplitude ranging from ground to V . This allows

CC

transients. When operating with V at 18 V, proper power

CC

the output of one channel to directly drive the input of a

second channel for master−slave operation. Each input has

a 30 kW pulldown resistor so that an unconnected open

input will cause the associated Drive Output to be in a

known low state.

supply bypassing must be observed to prevent the output

ringing from exceeding the maximum 20 V device rating.

Negative output transients are clamped by the internal NPN

pullup transistor. Since full supply voltage is applied across

http://onsemi.com

6

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]