Other functions of the ENUR register include saving the

ninth bit received in the data frame, enabling or disabling the

USART’s attention mode of operation and providing addi-

tional receiver/transmitter status information via RCVG and

XMTG bits. The determination of an internal or external clock

source is done by the ENUI register, as well as selecting the

number of stop bits and enabling or disabling transmit and

receive interrupts. A control flag in this register can also se-

lect the USART mode of operation: asynchronous or

synchronous.

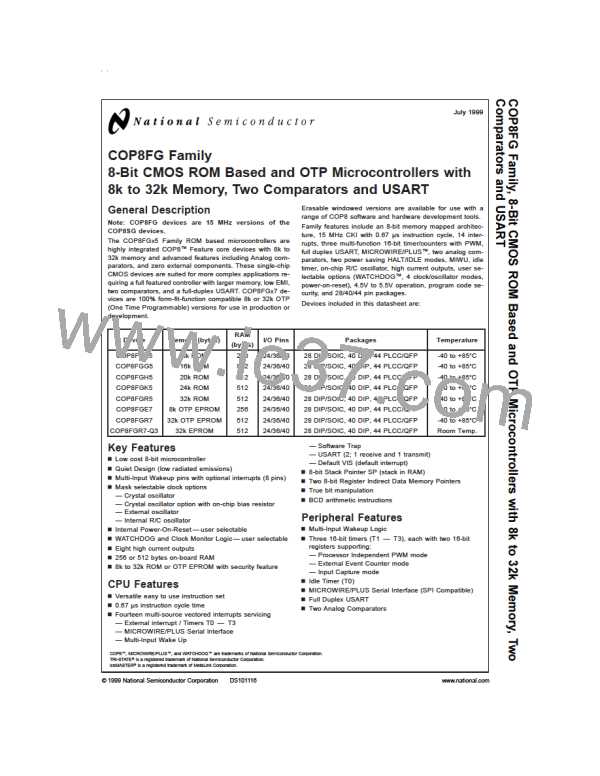

8.0 USART

Each device contains a full-duplex software programmable

USART. The USART (Figure 22) consists of a transmit shift

register, a receive shift register and seven addressable reg-

isters, as follows: a transmit buffer register (TBUF), a re-

ceiver buffer register (RBUF), a USART control and status

register (ENU), a USART receive control and status register

(ENUR),

a USART interrupt and clock source register

(ENUI), a prescaler select register (PSR) and baud (BAUD)

register. The ENU register contains flags for transmit and re-

ceive functions; this register also determines the length of

the data frame (7, 8 or 9 bits), the value of the ninth bit in

transmission, and parity selection bits. The ENUR register

flags framing, data overrun and parity errors while the US-

ART is receiving.

DS101116-39

FIGURE 22. USART Block Diagram

25

www.national.com

NSC [ National Semiconductor ]

NSC [ National Semiconductor ]